OCR technického popisu FK-1

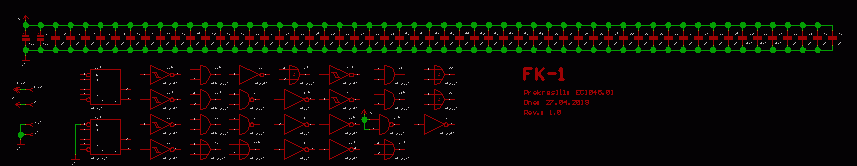

FK-1

TECHNICKÝ

POPIS

Technický popis počítače FK-1

- Stručná charakteristika počítače

- Pravidla používaná při popisu schémat

- Popis listu č. 1 PROCESOR

- Popis listu č. 2 PAMĚŤ

- Popis listu č. 3 VIDEO I

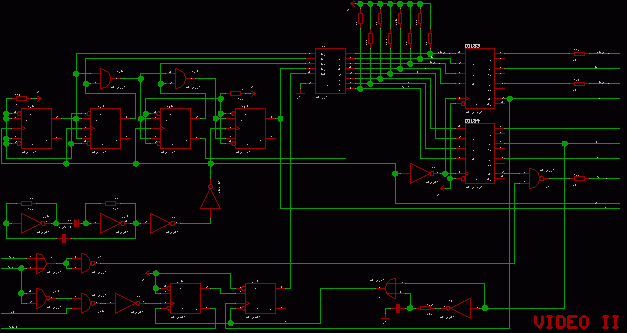

- Popis listu č. 4 VIDEO II

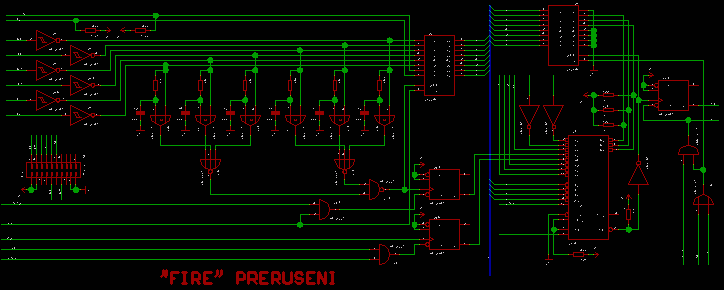

- Popis listu č. 5 PŘERUŠENÍ

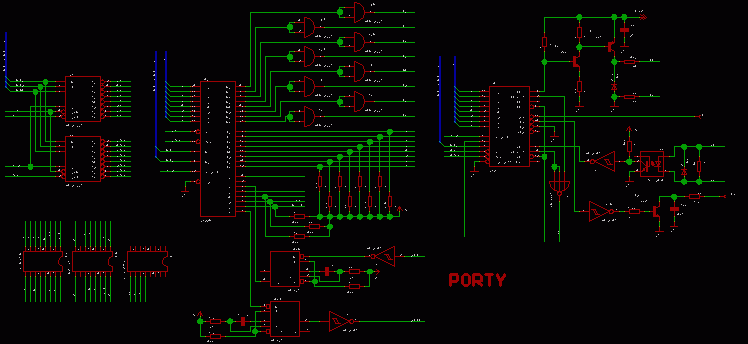

- Popis listu č. 6 PORTY

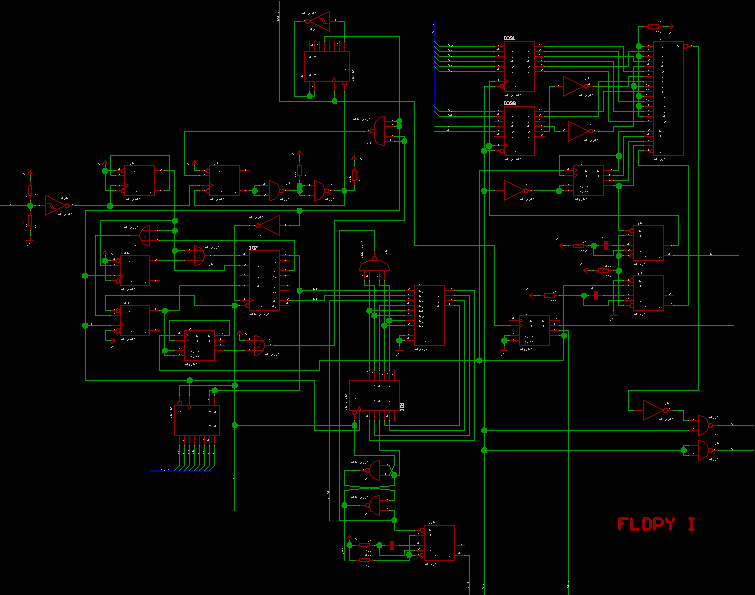

- Popis listu č. 7 FLOPY I

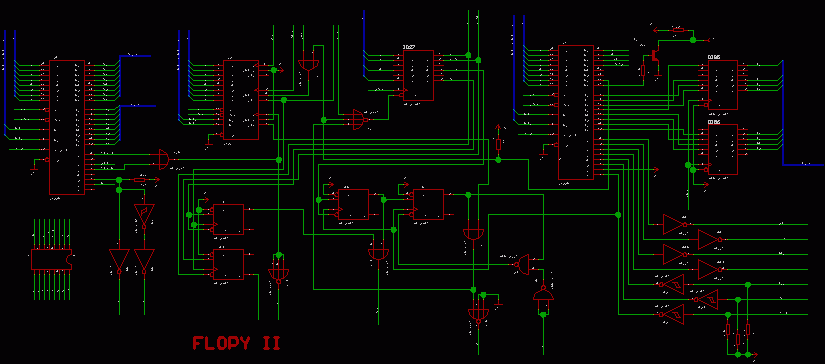

- Popis listu č. 8 FLOPY II

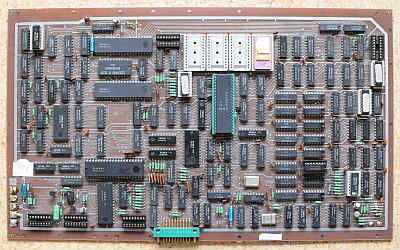

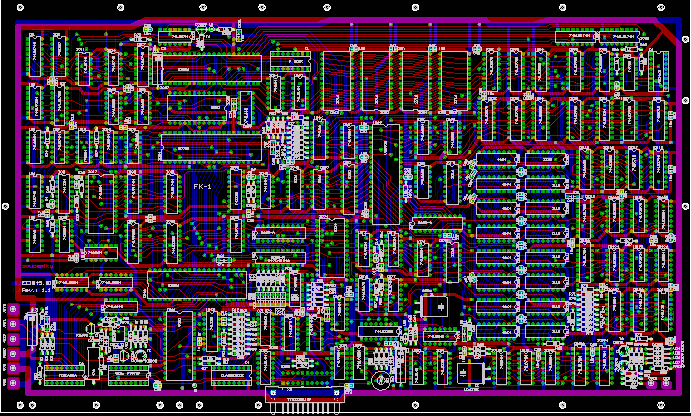

- Výkres osazení

- Elektrické schéma

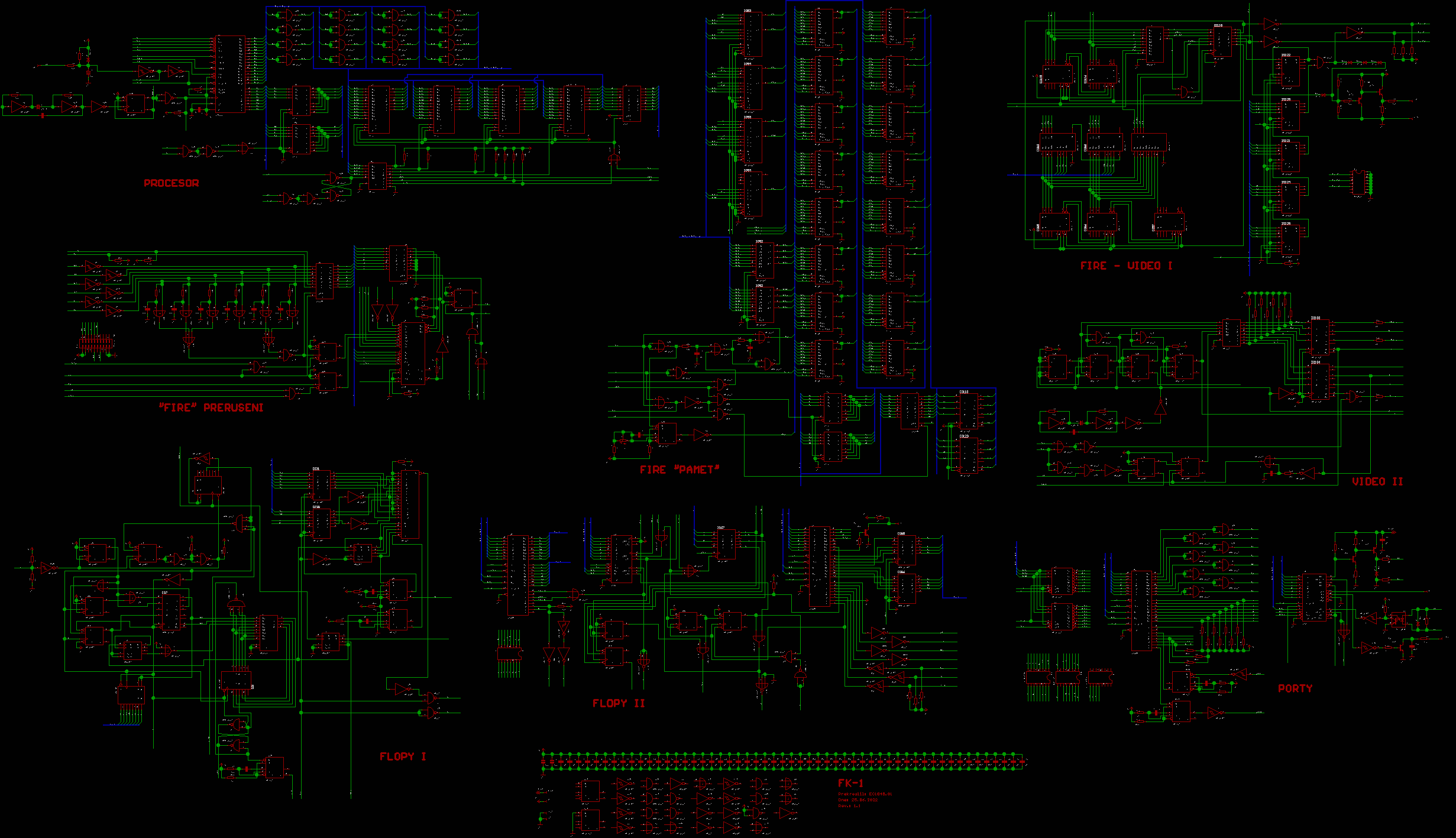

- Elektrické schéma č. 1 PROCESOR

- Elektrické schéma č. 2 PAMĚŤ

- Elektrické schéma č. 3 VIDEO I

- Elektrické schéma č. 4 VIDEO II

- Elektrické schéma č. 5 PŘERUŠENÍ

- Elektrické schéma č. 6 PORTY

- Elektrické schéma č. 7 FLOPY I

- Elektrické schéma č. 8 FLOPY II

- Elektrické schéma č. 0

- PROM

- BOOT EPROM

- TEST EPROM

- Dokumentace ke stažení

Pravidla používaná při popisu schémat.

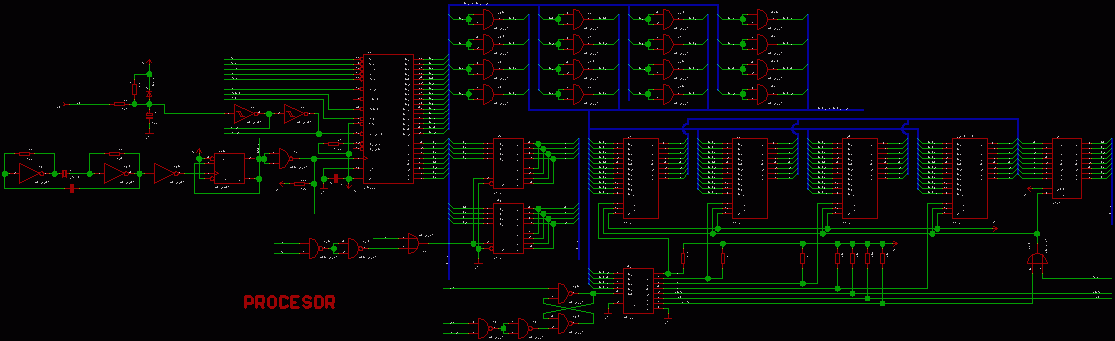

Popis listu č. 1 PROCESOR

- při čtení dat z periferií - je signál IORQ a RD

- při čtení vektoru přerušení - je signál IORQ a M1

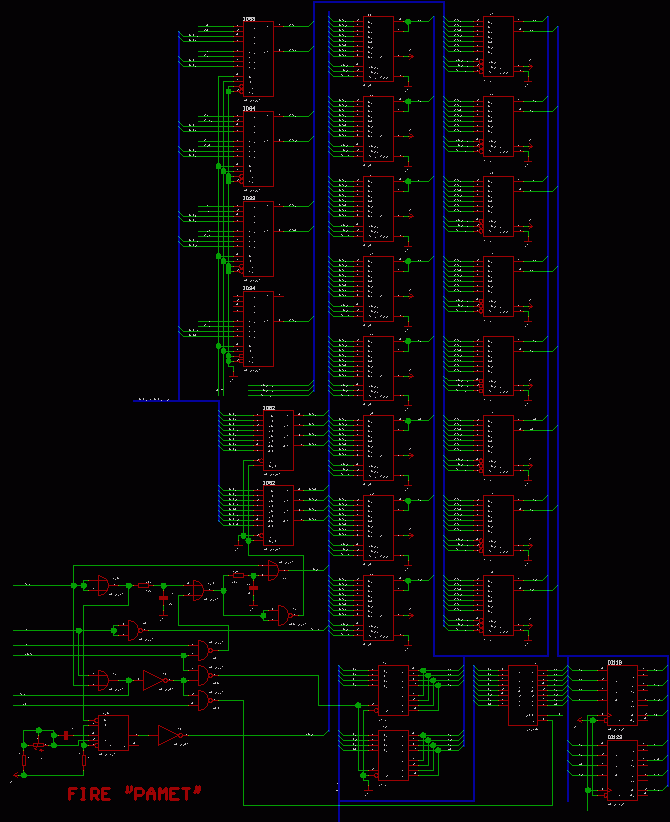

Popis listu č. 2 PAMĚŤ

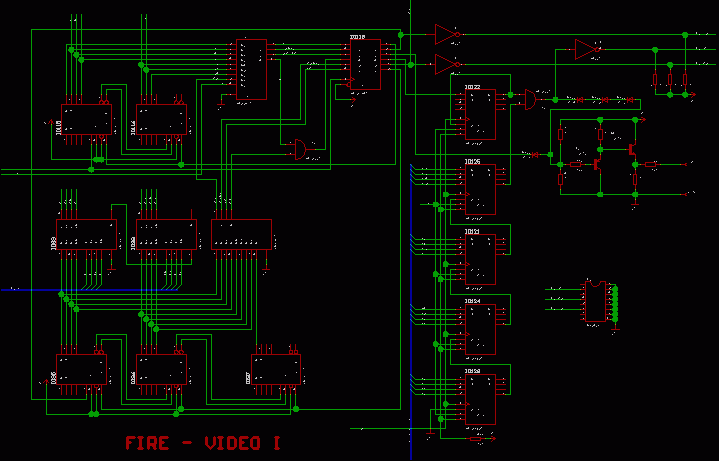

Popis listu č. 3 VIDEO I

Popis listu č. 4 VIDEO II

- Signál RAS přejde do nuly a zapamatuje do čipů adresu řádku

- Potom se změní signál A a multiplexor připojí adresu sloupců

- Pak přejde do nuly poprvé CAS

- Signálem L1 se po chvíli odpamatuje první bajt z VIDEORAM

- Pak se vrátí CAS do jedničky a změní se stránková adresa PG do jedničky

- Pak přijde CAS podruhé do nuly a odpamatuje se druhý bajt pomocí L2 do posuvného registru na listu č. 4

- Potom je ukončen RAS a tím cykl pro video

- pro procesor přejde B do jedníčky, čímž začne pracovat druhá polovina multiplexorů LS 253 na listu č. 2

- Pak se normálně vygeneruje RAS, změna A a CAS jako pro normální RAM a případně ještě signál WEG časovaný tak, aby byl jeho začátek před CAS

Popis listu č. 5 PŘERUŠENI

Popis listu č. 6 PORTY

Popis listu č. 7 FLOPY I

Popis listu č. 8 FLOPY II

- MEZERY (GAP)

- ADRESOVÉ ZNAČKY (ADRESS MARK)

- IDENTIFIKÁTOR SEKTORU (SECTOR IDENTIFIER)

- DATOVÝ BLOK (DATA BLOCK)

Přílohy:

- schémata jsou rozdělena na osm listů, číslovaných od 1 do 8

- integrované obvody jsou číslovány za písmenem E (E 13, E 35),

- vstupy příslušného integrovaného obvodu jsou označeny Číslem lomítkem následujícím po čísle obvodu. Například E 12/2 je vstup nebo výstup integrovaného obvodu číslo E 12 a vývod číslo 2 obvodu.

- Další součástky jsou označeny těmito písmeny a číslem.

| Z | piezorezonátor (krystal) | |

| R | rezistor (odpor) | |

| C | kondenzátor | |

| C | dioda | |

| VD | tranzistor | |

| X | konektor |

- vodorovná krátká tlustší čára značí zem, neboli 0V.

- šipka s nápisem +5 V znamená připojení na napětí +5 V.

- šipka, ve které je vepsáno číslo, značí šipku konektoru Xn.

- číslo obvodu je vepsáno buď v obvodu (v kroužku nebo bez) anebo v kroužku vedle obvodu.

- kroužek u šipky na kraji schématu a v něm číslo značí na jakém listu schémat signál pokračuje. U šipky je také název signálu. Tak například HCK a v kroužku 4, znamená signál „Horizontál Clock" - horizontální hodiny a přicházejí z listu schémat č. 4.

- V některých částech schématu je v obdélníčku nápis, popisující funkci okolních obvodů. Například ROM DEK (dekodér napětí ROM).

- tlusté spoje, z nichž vodorovně vychází spoje s označením signálů (např. DO, D1, D2 atd.) jsou vícenásobné signály, tak zvané sběrnice. Převážně jsou to DATA, ADRESA, PERIFERNÍ DATA PD,.

- Označení jako LS 14, LS 00 jsou zkrácené názvy integrovaných obvodů jako 74 LS 14, 74 LS 00. Místo těchto obvodů však mohou být použity ekvivalenty těchto obvodů, buď sovětské výroby anebo naše obvody například MH 74 ALS 00.

- Zvýraznění textu nahrazuje pruh nad signálem (např. MRQ) a značí invertovaný signál s aktivní úrovní Log. 0. Čte se jako NON neboli MRQ = MRQ NON.

- Na tomto listu jsou obvody okolo mikroprocesoru Z 80A. Vlevo nahoře je hodinový oscilátor řízený piezorezonátorem. Oscilátor kmitá na frekvenci 8 MHz. Oscilátor je tvořen z invertorů E 79, rezonátoru Z 1 a odporů R 63 a R 64, kondenzátoru C 9, který tvoří zpětnou vazbu. Za oscilátorem je zařazen frekvenční dělič dvěmi, 74 LS 74 E 77/6. Mohl by být použit rezonátor 4 MHz, ale ten se vyrábí jen ve velkém pouzdře a proto je použit malý krystalek 8 MHz.

- Frekvence 4 MHz z výstupu děliče E 77/6 je používáno i na listu č. 7 v obvodech připojených flopydisku.

- Hodinový vstup Z 80A E 66/6 potřebuje vyšší úroveň napětí, než jsou schopny generovat obvody řady 74 LS. Proto je frekvence 4 MHz zesílena hradlem E 76/11 a výstup hradla je přitažen k napětí +5 V odporem R 58 o hodnotě 330 Ohm. Tím dosáhne hodina skoro napětí +5 V.

- Mikroprocesor Z 80A E 66 má 16 adresových výstupů A 0 až A 15. Adresy jsou mnohokrát zatíženy a představují velmi dlouhé spoje. Proto jsou adresy zesíleny hradly LS 08, které jsou v obvodech E 47, E 67, E 68 a E 69. Adresová sběrnice AB (Adress Buffered) je pak rozvedena prakticky po celé desce.

- Na schématu je naznačeno i napájení mikroprocesoru Z 80A a to napětí +5 V na vývod E 66/11 a zem E 66/29. Napájení je blokováno keramickým kondenzátorem.

- Nulovací vstup Z 80A E 66/26 RES (Reset) je připojen na výstup hradla E 80 LS 14. Na listu č. 6 a č. 8 je potřeba signál RESET v opačné logické polaritě, je označen RES a vede z výstupu hradla LS 14 E 80/4. Vznik signálu RES je od tlačítka, z něhož přichází signál RTL přes ochranný odpor 100 ohm. Přes tento odpor se při stlačení tlačítka vybije kondenzátor C 2 20 M a na vstup E 80/3 LS 14 přijde nula. Nula se na tomto vstupu objeví i při zapnutí napájení a to do té doby, dokud se nenabije kondenzátor C 2 na napětí asi 1,6 V. Nuluje se tedy tlačítkem a nebo od zapnutí napájení počítače.

- Signál M1 E 66/27 je výstup Z 80A a nula na tomto výstupu označena tzv. FETCH cyklus instrukce anebo cykl potvrzení přerušení spolu se signálem IORQ.

- Signál M1 je používán ještě na listu č. 5 v obvodech přerušení.

- Signál M1 je pak sečten se signálem RD v hradle E 76/2, neboť pomocí tohoto hradla je vyráběn signál řídící směr otevření zesilovačů 3216 E 49 a E 50. Tyto zesilovače musí být otevřeny tak, aby jimi data procházela do mikroprocesoru Z 80A ve dvou případech:

signálu IORQ a současně RD nebo M1.

Právě plnění této logické rovnice zajišťují hradla 7437 E 76/2 a E 76/6 a hradlo LS 32 E 72/11.

- ostatní signály z levé strany mikroprocesoru mají tento význam:

NMI nemaskovatelné přerušení připojené na log. 1 neboli +5 V

BUSRQ žádost o DMA, která se nevyužívá opět připojeno na logl.

REF refreš pamětí vede na list č. 2

WAIT čekej - vede do obvodů vede na listu č. 4

MRQ žádost o přístup k paměti vede na listu č. 2

IORQ žádost o přístup k periferii, vede na listu č. 6

RD čtení, vede na list č. 2 a 6

WR zápis, vede na listy č. 2 a 6

INT přerušení od obvodu 3214 z listu č. 5

- všechny řídící signály Z80A jsou aktivní v nule.

- ze signálů z pravé strany mikroprocesoru jsme ještě nehovořili o DATECH. Data DO až D7 tvoří jedno osmibitové slovo neboli jeden byte.

Proto se mikropočítači FK-1 říká osmibitový. Datové sběrnice jsou u FK-1 dvě:

DB - Data Bus a ten jde na paměti EPROM (list č. 1, paměti RAM list č. 2) videoram a RAM

PD - Periferal Data, data pro periferie a ty jdou na obvody 8255, 8253, 8251 a na další registry pro připojištění periferií.

- U FK-1 je tedy oddělena sběrnice dat pamětí a sběrnice dat pro přídavná zařízení.

- No listu č. 1 vpravo nahoře jsou naznačeny čtyři paměti EPROM. Ve skutečnosti tyto čtyři obdélníky představují čtyři objímky pro integrované obvody s 24 vývody. V FK-1 jsou použity paměti EPROM o kapacitě 2KByte, typ 2716. Po malé úpravě by bylo možné použít i typy s dvojnásobnou kapacitou 2732, ale pro operační systém CP/M, který se natahuje z disku postačí docela jedna paměť 2716 E 65 a objímky pro E 64, E 63 a E 62 zůstávají volné.

- Paměť EPROM typ 2716 má jedenáct adresovaných vstupů A 0 až A 10 a osm datových výstupů Q 0 až Q 7. Tyto datové výstupy jsou od sběrnice DB odděleny zesilovačem 8282 E 51. Otevření výstupů tohoto zesilovače E 51 je řízeno nulou na jeho vstupu E 51/9 nazvaného OE (OUTPUT Enable). Na tomto vstupu je nula, pokud je současně nula na vstupech E 72/5 (signál MRD Memory Read) a současně nula na vstupu E 72/4 (signál EPROM). MRD je v nule pokud je MRQ a RD v nule a tento součin se získává na hradle LS 32 E 73 na listu č. 2.

- Pro čtení z pamětí EPROM je ještě nutné vybrat jednu ze čtyř pamětí E 62 až E 65. podle stavu adres A 12, 13, 14 a 15. Výběr pamětí závisí také na stavu signálu MAP (mapování pamětí), jak uvidíme později. Dekodér všech pamětí (pamětí EPROM až EPROM 3 a paměti RAM a paměti videoram - signál CRT (je tvořen pamětí PROM 74 188 E 46. Paměť má výstupy s otevřeným kolektorem a proto jsou k výstupům E 46 připojeny odbory R 37 až R43.

- Paměťový prostor mikroprocesoru Z 80A má kapacitu 64Kbyte, neboli 4x po 16KB. Mikropočítač FK-1 ale potřebuje adresovat celkem 64KB paměti RAM, 16KB paměti videoram a ještě paměti EPROM, pro které je pro jednoduchost vyhrazen celý prostor 16KB pro případ, kdy by byly použity 4 paměti EPROM po 4KB typy 2732. Proto jsou čtyři čtvrtiny adresovaného prostoru mikroprocesoru po 16KB rozděleny v závislosti na signálu MAP takto:

| MAP = 0 | MAP = 1 | čtvrtina |

| EPROM | RAM | 1. |

| VIDEORAM | RAM | 2. |

| RAM | RAM | 3. |

| RAM | RAM | 4. |

- Signál MAP se vyrábí v R-S klopném obvodu z hradel LS 00 E 29. Po zapnutí je díky signálu RES klopný obvod překlopen tak, že MAP = 0. Je to nutné, protože Z 80A začíná provádět program od nulové adresy a proto musí být na počátku adresovaného prostoru adresovaná paměť EPROM se zaváděcím programem. Když potřebuje program přistoupit ke spodní polovině RAM, provede takovou Instrukci, která generuje signál 6RD E 29/1 a klopný obvod se překlopí do stavu MAP = 1. Chce-li program opět pracovat s EPROM nebo VIDEORAM provede takovou instrukci, která generuje signál 5RD E 29/9 Tomuto přepínání adres pamětí se říká mapování.

Tím je ukončen výklad obvodů na listu č. 1.

- Jak již bylo řečeno FK-1 má kapacitu paměti RAM 64KB a k tomu navíc ještě 16KB paměti VIDEORAM, ve které jsou uloženy informace zobrazované na obrazovce.

- Pro paměť RAM jsou použity čipy dynamických pamětí 64KB, známé jako typ 4164 (sovětský typ RU 5) na listu č. 2 vpravo nahoře jako E 99 až E 106 (8 čipů). Pro paměť VIDEORAM jsou použity čipy 16KB známé jako typ 4516, neboli 16KB s na pájením pouze +5 V, na list č. 2 vpravo nahoře jako E107 až E 114 (sovětské značení RU 6).

- Dynamické paměťové čipy jsou charakteristické tím, že se do nich zadává adresa nadvakrát, což vede k úspoře počtu potřebných vývodů obvodu. Díky tomu jsou oba typy pamětí v pouzdrech pouze se 16 vývody. Nejprve se zadá spodní polovina adresy a to 8bit u RU 5 a 7bit u RU 6. Zadání spodní poloviny adresy je doprovázeno přechodem signálu RAS od nuly a zadání druhé poloviny adresy přechodem signálu CAS do nuly.

Jak uvidíme později pracují čipy RU 6 ve VIDEORAM v tzv. stránkovém módu, kdy se zadá jedním RAS společná adresa řádku a pak postupně dvěmi CAS dvě adresy sloupců pamětí. Ušetří se tak čas pro dodržení správného časového signálu RAS a přístup k VIDEORAM je rychlejší.

- Dva obvody LS 257, multiplexory dvou signálů na jeden výstup, slouží jako přepínače adres řádků (řádek ROW a z toho RAS = ROW Adress Strobe) adres sloupců COLOMN a z toho CAS.

- Dynamické paměti potřebují tzv. refreš, neboli obnovení obsahu paměti a to je nutné provést 128x za 2ms. U paměti RAM tuto refreš zajišťuje přímo procesor, který ve volném čase v každé instrukci vydá 7 bitů refrešovací adresy na A0 až A6 a současně signál MRQ a REF. U videoram je zase refreš zajištěna tím, že se paměť neustále čte do obvodů zobrazení na obrazovce a tím je zajištěna refreš VIDEORAM.

- Datové vstupy a výstupy čipů RAM, vývody 2 a 14 E 99 - E 106 sou spojeny a datové zesilovače 3216 oddělují čipy od sběrnice označené DB.

- U VIDEORAM jsou k zesilovačům připojeny pouze vstupy a čtení z čipů Videoram je uděláno složitější, protože informace čtená do procesoru se odpamatovává do registru 8282 E 71 a informace čtená pro zobrazení se odpamatovává do registrů LS 175 E 119 a 123 anebo přímo do posuvných registrů LS 295 E 124 na listu č. 3.

- Logické obvody, na listu č. 2 vlevo dole, zajišťují správné časování všech signálů pro paměť RAM a řízení zesilovačů dat směrem ke sběrnici mikropočítače DB. Časování signálů VIDEO RAM je na listu č. 4, kde jsou vyráběny signály RAS G, CAS G a WEG , kde G znamená grafika, protože zobrazení na obrazovce FK-1 je plná bodová grafika v rastru 512x256, ale o tom až na listu č. 4. Tam se také generují signály L1, A B pro obvody VIDEORAM.

- Signál RAS pro RAM generuje monostabilní obvod 74 123 E 78/13 a invertor LS 04 E 79. Monostabilní obvod je spouštěn sestupnou hranou na jeho vstupu E78/1, neboli sestupnou hranou signálu MRQ (žádost o paměť). MRQ je generován při čtení z RAM, při zápisu do RAM i při refreši doprovázené signálem REF. Monostabilní obvod vlastně zkracuje signál MRQ na konstantní šířku, danou velikostí RC členu C 13 a R 61 a konstantní šířka signálu RAS zajišťuje dodržení nabíjecího času (RAS Precharing Time) čipů RAM, který by jinak nebyl dodržen, protože u Z 80A jsou mezi signály MRQ jdoucími po sobě malé prodlevy.

- Hradlo 74 LS 00, čtyřnásobné dvouvstupové hradlo NAND plní funkci dekodéru důležitých signálů pro obvody RAM. Hradlo E 74/8 invertuje signál RD (čtení) a vyrábí tak vlastně signál zápis (WE) pro čipy RAM. Použití invertovaného RD místo běžného WR (zápis) z mikroprocesoru zajišťuje správné časování signálu WE před signálem CAS a tím správné otevírání výstupů čipů RAM (Cykl Early Write). Hradlo E 74/11 vyrábí povolovací signál pro průchod MRQ hradlem LS 32 E 73/5. Toto hradlo pak generuje signál pro přepnutí multiplexorů E 82 a E 92 a generování signálu CAS. K povolení je třeba, aby na E 74/11 byla nula a ta je když je RAM i REF na jedničce, tedy kdykoliv je vybrána RAM (adresový dek na listu č. 1) a není Refreš. Při refreši se tedy nepřepínají adresy a ani není generován RAS.

- Hradlo LS 32 E 73/11 generuje součin MRQ a RD nebo li signál MRD (Memory Read). Hradlo LS 04 E 79 tento signál invertuje a hradlo LS 00 E 74/6 pak tvoří součin mezi MRD a CRT, neboli signál říkající, že se čte z části paměti nazývané VIDEO-RAM. Výstup E 74/6 pak otevírá výstupy registru 8282 E 71 směrem na sběrnici DB, neboli do Z 80A.

- Hradlo LS 00 E 74/3 vyrábí signál, ale při RAM = 1, neboli otevírá výstupy zesilovačů 3216 E 70 a 75 při čtení z RAM do mikroprocesoru Z 80A.

- K dokončení popisu logiky časování signálů pro RAM chybí ještě vysvětlení, co se stane po generování signálu RAS. Od MRQ se nahodí monostabilní obvod a je generován RAS.

- Od MRQ se po zpoždění, daném R 56 a C 12 generuje signál pro přepnutí multiplexorů (vstupy S E82/1 a E92/1). Tím se k adresovým

vstupům připojí vyšší část adres. Multiplexory totiž přepínají adresu takto:

při: E 82 E 92

| S = 0 | A0 | A1 | A2 | A3 | A4 | A5 | A6 | A15 |

| S = 1 | A7 | A10 | A9 | A11 | A13 | A12 | A8 | A14 |

- na pořadí adres nezáleží a při S = 0 musí být na vstupech čipů RU 5 adresa A 0 až A 6 (7 bitů) pro správné provádění refreše. Jak již bylo řečeno, při refreši se multiplexory nepřepínají.

- po přepnutí multiplexorů LS 257 se signál z výstupu LS 32 E 73/6 zpožďuje RC členem R 57 a C 14 a vznikne signál CAS pro čipy

RAM. Signál

- k dokončení popisu listu č. 2 nám chybí ještě popis části s čipy RU 6, neboli VIDEORAM. Jak již bylo naznačeno, čtou se z VIDEORAM vždy dva bajty po sobě v tzv. stránkovém módu.

- první bajt, při prvním CASG se odpamatovává od registru LS 175 E 119 a E 123 s náběhem signálu L1.

- druhý bajt (signály R0 až R7) jde přímo do posuvných registrů videa, kam se přepisuje společně se zapamatovanými R8 až R16. Při druhém signálu CASG.

- při čtení do mikroprocesoru Z 80A se čtená data odpamatovávají do registru 8282 E 71.

- přepínání adres pro čipy RAM je u VIDEORAM komplikovanější než u RAM. VIDEORAM je totiž paměť s dvojím přístupem (dvojbránová paměť - DUAL PORT MEMORY) a musí mít do ni přístup jak Z 80A, tak časová základna VIDEOOBVODU, která určuje signály H2 až H32 a V2 až V128 (Vertikální a Horizontální adresy, která buňka paměti se bude zobrazovat na obrazovce.

- řízení multiplexoru mají na starosti signály A a B, kde A vlastně časuje podle RAS a CAS, jako u RAM a B rozlišuje přístup procesoru Z 80A od přístupu z obvodu Videa. Neboli procesor CRT.

- tím je ukončen popis listu č. 2 PAMĚŤ, protože singály pro VIDEORAM jsou generovány v časové základně na listu č. 4.

- na listu č. 3 jsou obvody kolem videa, neboli kolem zobrazení informací na stínítku obrazovky. V levé polovině je časová základna vytvářející časové posloupnosti signálů synchronizace (synchronizační impulsy se nazývají HS a VS) a generují adresy H a V pro VIDEORAM. V pravé polovině je 16 bitový posuvný registr videa (4xLS 295) a generace signálů synchronizace a signálů pro zatmění obrazovky.

- Vysvětleme si nejprve základy pro tvorbu jednotlivých zkratek signálů, protože pak bude vše jasnější:

| H | Horizontální - vodorovný neboli vše co souvisí s vodorovným pohybem paprsku po obrazovce |

| V | Vertikální - svislý, neboli pohyb paprsku ve svislém směru |

| HCK | Horisontal Clock - horizontální hodiny v taktu jednoho znaku, neboli osmi bodů grafiky |

| S | Synchronizace HS a VS |

| B | Blank - zatmívání NB a VB neboli čas, kdy obrazovka nesmí svítit |

| AZJ | Alfanumerická Zobrazovací Jednotka - speciální monitor firmy Zbrojovka Brno, který se již nepoužívá |

| ROM | Read Only Memory - paměť s pevným obsahem daným naprogramováním při výrobě |

| L | Load, neboli náplň |

| CVID | Kompositní videosignál obsahující Video, HS a VS i Blank |

| VID | Videosignál znamenající Černá/bílá |

| R | Rest čítačů, neboli okamžik vynulování H čítačů (RH) a V čítačů (RV) |

- Signál HCK má frekvenci 12,5 MHz děleno osmi, protože se vždy zobrazuje osm bodů vedle sebe. Těchto osm bodu se zobrazuje 64krát, neboli je na jedné lince 512 bodů.

- HCK inkrementuje horizontální čítač tvořený dvěmi obvody LS 193 E 115 a E 116: Paměť ROM 74 S 287 E 117 hlídá obsah těchto čítačů a při určité maximální hodnotě vydá signál RH, který čítače E 115 a E 116 vynulují. V výstupů čítačů jsou, pak do multiplexorů pro videoram vedeny adresy H2 až H 32.

- Signálem HS AZJ je pak inkrementován vertikální čítač tvořený třemi, čítači LS 193, a Registr LS 174 E 118 pouze od pamatovává výstupy z paměti ROM a odstraňuje tak přechodové hazardní stavy, kdy se při přepínání adres na vstupech ROM objevují špičky na jejích výstupech Y1 až Y 4. Jinak registr nikterak nemění signály označené na jeho vstupech.

- Podobně jako horizontální čítač generuje vertikální čítač adresy pro zobrazení. Protože je však někdy nutné posunout všechny informace na obrazovce ve svislém směru (tzv. rolování -u psacího stroje vlastně posuv válce o řádku) je na výstupech z vertikálního čítače připojena sčítačka, která vlastně umí spočítat osmibitový součet čísel A a B. Když je potom potřeba posunout informaci, např. o jednu linku, nemusí se obsah celé VIDEORAM přepisovat programem a stačí přivést na druhé vstupy sčítaček LS 283 E 89 a E 90 číslo PB 0 až PB 7 o jedničku větší a informace se pak z VIDEORAM vybírá posunuté o jednu linku. Tomuto říkáme Hardware Rolling.

- Podobně jako u horizontálních čítačů hlídá paměť ROM 74 S 571 E 98 obsah vertikálního čítače a při dodržení čísla 312 linek vynuluje vertikální čítač a začíná se opět nový snímek od nuly. Paměti ROM E117 a E 98 generují pak se znalostí obsahu čítačů H a V všechny potřebné signály pro horizontální a vertikální synchronizaci obrazovky a pro zatmívání obrazovky. Výhodou použití pamětí ROM je možnost časové změny časování při přechodu na jiný typ monitoru s jiným časováním.

- Hradlo LS 08 E 126 dělá součet horizontálního a vertikálního zatmívacího signálu a generuje tak společný zatmívací signál pro kompositní videosignál.

- Signály pro synchronizaci jednotky AZJ, připojované ke konektoru X 6 mají jiné časování než pro TV monitor a proto jsou pamětmi ROM zpracovány zvlášť. Jsou nazvány s indexem AZJ.

- Výstupní obvody pro AZJ jsou tvořeny vysílači s otevřeným kolektorem 7406, protože AZJ má výkonové zakončení malými odpory.

- Registr LS 295 E 112 pouze synchronizuje signál zatmívání se signálem L 2 a povolení videa je provedeno na výstupu tohoto registru hradlem LS 08 E 126/8.

- Šestnáctibitový registr je naplněn v okamžiku L 2 synchronně s hodinami SCK z výstupů paměti VIDEORAM (list č. 2.). Díky stránkovému módu čtení VIDEORAM jsou z paměti připraveny vždy dva bajty najednou. Po naplnění se informace v registrech LS 295 E 120, 121, 124 a 125 posunuje ven v rytmu hodin SCK a vystupuje z E 125/10 videosignál do převodníku tvořeného transistory a diodami, který převádí signály synchronizace a videa na potřebné úrovně.

- Tím je ukončen popis listu č. 3 VIDEO I.

- Na listu č. 4 je časová základna pro řízení všech obvodů videa. Časové řízení těchto obvodů je složité, protože při současném zobrazování a současné spolupráci VIDEORAM s procesorem je velice málo času a časování musí být značně přesné, aby nedocházelo ke kolizím.

- Zdrojem frekvence je krystalový oscilátor o frekv. 12,5 MHz tvořený resonátorem Z2 a invertory S 04 E 130. Tím vznikne signál SCK (Schift Register Clock) neboli hodiny posuvných registrů.

- Frekvence z oscilátoru je dělena 16 v rychlém čítači sestaveném z J-K klopných obvodů 74 S 112 E 128 a E 129 a hradel LS 08 E 126.

- Výstupy čítače jsou do paměti ROM 74188 E 127 a podle obsahu paměti ROM jsou generovány tyto signály:

| RAS G | Signál RAS pro Videoram |

| A | Signál pro přepnutí multiplexorů 74 LS 153 E 83, 84, 93 a 94 na listu č. 2. Tento signál přepíná adresy VIDEORAM mezi RAS G a CAS G. |

| CAS G | Signál CAS pro VIDEORAM |

| PG | Page stránka, neboli bit adresy, který se mění z nuly na jedničku mezi dvěma CAS ve stránkovém módu čtení z VIDEORAM. |

| B | Signál říkající, že přístup k VIDEORAM má procesor Z80A |

| L1 | Náplň pomocný registr (2xLS 175 na listu č. 2) |

| L2 | Náplň 16 bit registr posuvný |

| WEG | Povolení k zápisu do čipů VIDEORAM |

| END | Konec přístupu procesoru a neboli shození signálu WAIT |

| HCK | Horizontální hodiny pro H čítač na listu č. 3 |

| WR, MRQ | Řídící signály z Z 80A |

| CRT | Výběr paměti VIDEORAM z dekodéru na listu č. 1 |

| WAIT | Čekej pro procesor Z 80, který musí počkat, než bude dokončen cykl spolupráce Z 80A a VIDEORAM. |

- Každý cykl paměti a VIDEA je rozdělen na dvě části. Každý cykl trvá 16 hodinových impulsů hodin SCK. Jedna část je vyhrazená (delší) pro VIDEORAM a druhá kratší pro procesor Z 80A. Normálně se druhá část neuplatňuje. Žádost o spuštění této části je splněna je li najednou signál CRT=1 a MRQ=0. Pak vznikne na výstupu hradla LS 00 E 132/3 nula = RQ. Na výstupu invertoru S 04 E 130/12 vznikne jednička a nastaví se do jedničky klopný obvod typu D LS 74 E 131/5. Na jeho výstupu Q E 130/6 vznikne signál WAIT a do té doby musí mikroprocesor Z 80A čekat na skončení signálu WAIT. Náběžná hrana signálu PG je shodou okolností umístěna tak, že je použita pro testování zda přichází žádost o VIDEORAM. Je-li první klopný obvod nastaven do jedničky, přepíše se při náběhu PG jednička i do druhého klopného obvodu a jeho výstup Q E 131/9 oznámí paměti ROM E 127, že má generovat i signály druhé části cyklu VIDEORAM. Jako poslední signál pro VIDEORAM skončí signál B a ten se zderivuje podle průběhu nakreslený vlevo dole a vznikne signál END o ten ukončí vynulováním klopného obvodu i signál pro paměť ROM. Tím je spolupráce s procesorem Z 80A jednak synchronizována a jednak ukončena, aby nemohla proběhnout podruhé, a musí se čekat znovu na RQ. Synchronizace je nutná, protože jinak by při vstupech do VIDEORAM na obrazovce problikávala interference mezi cykly videa a procesoru.

- Signál WR z procesoru je logicky vynásoben se signálem MRQ z procesoru a vznikne-li z ROM E127 signál WEN určující správný časový okamžik zápisu do Videoram vyrobí hradlo NAND E 132/11 signál povolení zápisu WEG. Některé signály do VIDEORAM jsou tlumeny odpory 33 Ohm, aby nedocházelo k zákmitům na dlouhých vodičích na desce plošného spoje.

- Nyní si popíšeme průběhy cyklů VIDEORAM. Musíme si uvědomit, že druhá část pro procesor je povolena jen tehdy, je-li na vstupu ROM E 127/14 jednička, neboli je li žádost z procesoru Z80A.

- Tím je ukončen popis listu č. 4 VIDEO II.

- Přerušení je u mikropočítače systém, kterým si přídavná zařízení zajišťují rychlou obsluhu programem. Základem je vždy žádost o přerušení (Interrupt Reguest) a přerušení z více míst obvykle vyhodnocuje řadič přerušení, který určí důležitost žadatele a zamezí konfliktům mezi současně vzniklými žádostmi. Takový řadič pak obvykle generuje tzv. vektor přerušení, nebo li ukazatel adresy, na které je uložena příslušná rutina obsluhy přerušení pro dané zařízení.

- Mikroprocesor Z 80 má tzv. sériový přerušovací systém ale pouze ve spojení s periferními obvody pro Z 80A. V mikropočítači FK-1 jsou ale použity převážně obvody rodiny mikroprocesoru Intel 8080 A a ty mají paralelní přerušovací systém. Naštěstí má Z 80A tři módy přerušení, z nichž jeden umožňuje zpracovat paralelní přerušení od obvodů Intel.

- Jako řadič přerušení je použit obvod MH 3214 patřící právě k mikroprocesoru 8080 A. Tento obvod E 54 má osm vstupů pro žádosti o přerušení označené jako R 7 (nejvyšší priorita) až R 0 (nejnižší priorita). Žádosti o přerušení jsou u FK-1 tyto:

| R 7 | DR | přerušení od požadavku dat z flopydisku |

| R 6 | TOUT | přerušení při překročení časů při obsluze flopydisku |

| R 5 | OVFL | přerušení při ukončení přenosu dat z flopydisku |

| R 4 | RTC | přerušení od reálného času, každých 20 ms |

| R 3 | MYŠ | přerušení od grafické periferie nazvané MYŠ |

| R 2 | R 2 | přerušení od sériového přenosu obvodu 8251 |

| R 1 | KI | přerušení od klávesnice |

| R 0 | PI | přerušení od tiskárny |

- Obvod MH 3214 umí generovat jen tříbitový vektor přerušení na svých výstupech A 0, A 1, A 2. Tento vektor je pak zapamatován do osmibitového registru 8282 a je doplněn nulou v nejnižším datovém bitu D 0 a nulami v bitech dat D 4 až D 7. Procesor Z 80A si pak při obsluze přerušení, při signálech Ml a IORQ ( viz list č. 1) přečte na datovou sběrnici obsah registru vektoru a tento vektor pak použije při výpočtu adresy, kde začíná rutina přerušení.

- Klopný obvod LS 74 E 77 si zapamatuje krátkou impulsní žádost o přerušení (signál INT do Z 80A) a po skončení cyklu, nazývaného INTA (potvrzení přerušení) je vynulován právě součinem signálů IORQ a M1, což u Z 80A znamená právě cykl INTA.

- Na listu č. 5 vlevo nahoře je obvod generující přerušení od myši. Myš má dva impulsní výstupy A a B pro každou osu pohybu X a Y a dva výstupy signálů z tlačítek T1 a T 2. Počítání impulsů od pohybu v osách je u FK 1 zajištěno programově a proto je nutné jednak, aby mikroprocesor věděl, kdy se jakýkoli stav vstupních signálů změnil, a jednak si pak program musí zjistit skutečný stav signálů po změně. Podle vzájemných fází změn signálů z os pak program vyhodnotí směr změny anebo změnu stavu tlačítka.

- Změnu zjišťují derivační obvody sestavené z hradel LS 86 E 55 a 56 a sčítací obvody derivačních impulsů, hradla LS 27 E 58 a hradlo LS 00 E 61. impuls od změny jakéhokoli stavu signálů nastaví klopný obvod LS 74 E 59 a z jeho výstupu Q E 59/8 vede žádost o přerušení na vstup R 3 řadiče MH3214. Program potom instrukcí s adresou generující signál přečte obsah registru 8282 E 53, do kterého se odpamatuje nový stav tlačítek. Tento registr signály ze vstupu invertuje.

- Povolení přerušení od myši je signálem IE MYŠ (Interrupt Enable) a ten vede z portů řadiče flopydisku. Signálem RD 7 se také žádost o přerušení ukončí, neboť je vynulován klopný obvod E 59/8.

- Podobně pracuje klopný obvod LS 74 E 59/6, který generuje přerušení každých 20 ms od vertikálního synchronizačního impulsu videa VS. Přerušení je povoleno signálem IERTC a nulováno signálem WR 7 z dekodéru adres portů.

- Řadič přerušení 3214 je připojen i na spodní čtyři datové bity datové sběrnice PD. Pomocí instrukce zápisu do portů, generující signál 6 WR (E 54/23) zapisuje program do řadiče číslo, které říká jaká nejvyšší úroveň přerušení je povolená. Priorita žádostí je však pevná. Po každé žádosti a jejím zpracování je nutné řadič 3214 znovu inicializovat právě zapsáním povolené úrovně pomocí datových bitů PD 0 až PD 3.

- Výstupy A0 až A2 z řadiče, neboli výstupy vektoru jsou s otevřenými kolektory a proto jsou zakončeny odpory na + 5 V.

- Hradlo LS 08 vyrábí součet signálů RES a INTA pro nulování klopného obvodu E 77 (signál RI - Reset Interrupt).

- Hradlo LS 32 E 81/3 vyrábí negativní signál INTA pro nulování klopného obvodu, nulování některých obvodů řadiče flopydisku na listu č. 8 a pro otevření třístavových výstupů registru vektoru 8282 E 52.

- Tím je ukončen popis listu č. 5 PŘERUŠENI.

- Vlevo nahoře je dekodér portů, neboli dekodér adres A4, A5 a A6 podle nichž se odlišují adresy portů. V některých případech je ještě v rámci této adresy více portů (například v obvodu 8255) a ty se potom ještě odlišují adresami A0 a A1.

- Horní dekodér 74 LS 138 je povolen signálem IORQ E 32/4 a signálem RD E 32/5. Oba dekodéry jsou povoleny neaktivním stavem signálů RESET. Výstupní signály dekodéru jsou nazvány RD 0, RD 1 až RD 7. Tento dekodér tedy adresuje vstupní porty mikroprocesoru, ze kterých se čtou informace.

- Druhý dekodér je místo signálem RD povolován signálem WR a adresuje tedy výstupní porty. Dekódování adres je u FK-1 trochu neobvyklé, protože se u přídavných obvodů (8253, 8255 a 8251) nepoužívají povolovací vstupy CS a místo toho se dekódují přímo signály RD a WR pro každý obvod zvlášť. To přináší jisté výhody.

- Adresy portů jsou přiřazeny takto:

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | signály | adresa | HEX |

| X | 0 | 0 | 0 | X | X | X | RD a WR 0 | 00 | |

| 0 | 0 | 1 | RD a WR 4 | 10 | |||||

| 0 | 1 | 0 | RD a WR 2 | 20 | |||||

| 0 | 1 | 1 | RD a WR 6 | 30 | |||||

| 1 | 0 | 0 | RD a WR 1 | 40 | |||||

| 1 | 0 | 1 | RD a WR 5 | 50 | |||||

| 1 | 1 | 0 | RD a WR 3 | 60 | |||||

| 1 | 1 | 1 | RD a WR 7 | 70 |

- Obvod paralelních portů 8255 E 40 slouží pro připojení klávesnice a tiskárny

- Tiskárna má konektorové signály označené písmenem T a je na konektoru X2.

- Klávesnice má signály označené písmenem K a je na konektoru X 4.

- Pro tiskárnu je použit port A obvodu 8255 a je naprogramován do módu 1. Pomocné signály pro tiskárnu jsou STBP - Storbe Data a tento výstupní signál je zkrácen monostabilním obvodem LS 123 E 42/5 na potřebnou délku. Vstupní signály do portu tiskárny jsou:

| PE | konec papíru |

| ERR | chyba |

| ACK | potvrzení o ukončení činnosti tiskárny |

- Port PB obvodu E 40 je použit jako vstupní, v módu 1, pro vstup z klávesnice. Vstupy z klávesnice jsou ošetřeny odpory. Signál vzorku STBK je opět zkrácen druhou polovinou LS 123 E 42. Z počítače FK-1 je klávesnice také napájena napětím +5 V. Výstupní bity portu 8255 E 40 označené PC 0 a PC 3 generují žádost o přerušení od klávesnice KI a žádost od tiskárny PI.

- V druhé polovině schéma je obvod 8251 A, který pracuje u FK-1 jako sériový port s výstupem do proudové smyčky 20 mA. Tento obvod je klasický UART pro asynchronní přenos. Synchronní přenos není u FK-1 možný. Zdrojem přenosové frekvence, vlastně 16x vyšší frekvence, kterou potřebuje obvod 8251 je časovač 8253 v řadiči flopydisku. Přenosová rychlost je tedy programovatelná programem. Protože proudová smyčka, nepotřebuje ovládací signály pro modem, je většina těchto vstupů a výstupů obvodu 8251A (CTS, DSR, DTR) nepožity.

- Vstupy řadiče přerušení 3214 jsou plně obsazeny a tak přerušení od přijmutého znaku RxC a vyslaného znaku TxC jsou u obvodu 8251 A sečteny pomocí hradla LS 27 E 58/8 a vedeny do MH 3214 jako R2. Program potom musí sám rozlišit, o jaké přerušení se jedná.

- Vysílaná data z výstupu UART E 41/19 nazvaná TxD jsou pak převedena na proudový signál převodníkem z tranzistorů T1 a T2 a proud smyčky je určen velikostí odporu R4 470 Ohm.

- Přijímaná data jsou oddělena optoisolátorem E22 WK164 14 a jeho výstup je ještě tvarován tvarovačem LS 14 E 21/4 a ty pak vstupují do vstupu RxD E 41/3.

- Signál DTR E 41/24 je určen jako pomocný výstup pro připojení reproduktoru přes tranzistor R5.

- Obvod 8251A potřebuje ke své činnosti hodiny CLK E 41/20 o ty jsou přivedeny z děliče u obvodů flopydisku na listu č.7.

- Oba obvody na listu č. 6 jsou směrem ke sběrnici připojeny standardním způsobem. Data jsou připojena na datovou sběrnici označenou jako PD. Adresové bity A0 až A1 volí u obvodu 8255 vnitřní registry PA, PB, PC a řídící port. Adresový bit u 8251 A podle stavu A 0 jeden ze dvou vnitřních registrů tohoto obvodu.

Signál RES s aktivní úrovní jedna umožňuje vynulovat oba porty a nastavit je tak po zapnutí do známého stavu.

Jak již bylo řečeno, jsou signály výběru CS uzemněny a dekódování portů je provedeno tak, že se dekódují přímo signály RD a WR pro každý obvod zvlášť.

Tím je ukončen popis listu č. 6 tak zvaných PORTŮ.

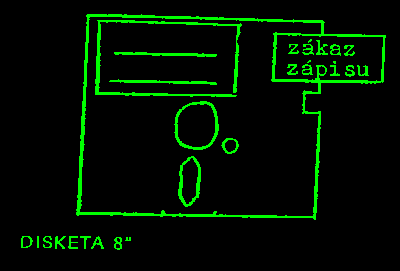

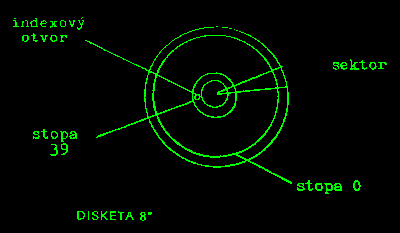

- Ke správnému pochopení těchto schémat je nejprve nutné znát principy záznamu a formátu na disketách z dodaných materiálů. Na disketě je záznam proveden v několika stopách a mechanika disku vystavuje postupně hlavu po těchto stopách. Vystavení se řídí směrem pohybu hlavy a signálem krok (STEP a DIR). Na každé stopě je pak zaznamenáno několik sektorů, dejme tomu 26 sektorů po 128 bytech. Aby bylo možno jednotlivé sektory poznat od sebe, je před každým sektorem nahráno tzv. záhlaví, ve kterém je číslo sektoru spolu s dalšími identifikačními údaji uvedeno. Řadič flopydisku musí tedy před čtením sektoru anebo před zápisem do sektoru nalézt záhlaví a pak teprve může provést zápis nebo čtení. Pro řadiče flopydisku se obvykle používají složité řadiče, které jsou vlastně jeden složitý integrovaný obvod. V období vzniku FK-1 nebyl však takový řadič k dispozici. Teprve inovovaný model FK-2 bude mít integrovaný řadič flopydisku INTEL 8272A.

- Řadič u FK-1 je realizován z běžných TTL obvodů doplněných o časovač 8253 a obvody portů 8255A.

- V levém horním rohu listu č. 7 jsou vstupní obvody sériových dat z flopydisku, které se nazývají RD (Read Data). Pomocí čtyřech klopných obvodů LS 74 E4 a E8 a děliče frekvence 74164 E 48 a dalších jsou z dat separovány datové a hodinové impulsy. Ty jsou potom synchronizovány v registru 74175 E7. Vznikají tak dva nezávislé signály D DAT a C DAT, neboli data a hodiny zvlášť. Pro rozpoznání speciálních značek v záhlaví adresy a dat na flopydisku jsou totiž použity triky s chybějícími hodinami, tzv. Missing Clock. Proto je nutné vyhodnocovat zvlášť průběh hodin a zvlášť průběh dat.

- Paměť PROM 74S287 E6 tvoří dvoubitový sériový komparátor, který porovnává přicházející průběhy C a D DAT a hledá v nich značku DAT a nebo značku ADRESY. Která značka je hledána a to říká stav signálu RDM (Read Data Mark) z portu 8255.

- Jakmile sériový komparátor značku pozná, vydá impuls na výstupu hradla LS 20 E 2/6 a ten zpustí monostabilní obvod LS 123 E 38/4. Výstup z tohoto obvodu pak naplňuje obvod paralelních portů 8255 na dalším listu daty, která přicházejí se sériově paralelního přechodníku dat z flopydisku, obvodu LS164 E 36. Současně se po nalezení značky překlopí R-S klopný obvod E 15 a vydá signál SYN, který synchronizuje všechny další časové operace.

- Signál SYN se také vrací zpět do sériového komparátoru značky (El/11) a do té doby začne hradlo LS 20/6 vydávat impulsy po každých 8 bitech sériově přijatých dat do registru LS 164 E 36. Tak vznikají i impulsy STB a data se paralelně dostávají do portů a odtud si je přebírá procesor.

- Vpravo nahoře je vlastně zcela inverzní obvod, obvod zápisu Základem zapisovacích obvodů je čítač 7493 A E18, který čítá od nuly do patnácti. Jeho čtyři výstupy QA až QD přepínají vstupy multiplexoru 74150 E 17. Na vstupech tohoto multiplexoru jsou připravena data W0 až W7 a současně hodiny. Hodiny jsou připraveny tak, že některé bity jsou pevně jedničkové a dva bity C 3 a C 4 jsou proměnné. Tyto proměnné bity hodin slouží právě pro zápis tzv. chybějících hodin ve značkách. Data W0 až W7 a bity hodin C 3 a C 4 přicházejí z paralelních portů na listu č. 8.

- Když se napíše poslední bit sériových dat, změní se QD E18 zpět do nuly, nahodí se klopný obvod E123 a vydá signál ACK, který oznámí paralelním portům, že mají připravit další data.

- Zesilovače 7438 E 13 zesilují jednak signál povolení zápisu WR na WE a jednak data do disku správnou šířku, je multiplexor E 17 vzorkován výstupem monostabilního obvodu E 9/12 impulsy asi o délce 600 ns.

- Dělič 7493 A vyrábí z frekvence 4 HMz frekvenci 2 MHz nazvanou FC pro obvod 8251 na listu porty a také frekvenci 1 MHz pro časovač 8253.

- Dělič 7493 A E5 funguje jako časový hlídač, hlídá dobu, po kterou jsou signalizovány chybějící hodiny ve značce (Missing Clock) nulou na výstupu klopného obvodu 74 LS 74 E 4/9. Tyto hodiny smějí chybět jen po dobu tří hodin, chybějí-li hodiny déle je separátor přepnut na opětovné zasynchronizování na přijímaná data z disku.

- Signál RE (Read Enable) je povolení čtení s disku a odblokovává všechny důležité obvody separátoru a dekodéru značek.

- Tím je ukončen popis listu č. 7 FLOPY I.

No tomto listu jsou zbývající obvody a řadiče. Vlevo je obvod paralelních portů 8255A, pracující v módu 1 a tento obvod zpracovává paralelní data čtená z flopydisku (DR 0 až DR 7 a signál STB) a data zapisovaná na flopydisk (W0 až W7 signál ACK).

- Při čtení přijde signál STB z listu č. 7 a ten zapíše data do portu PB 0 až PB 7. Současně je na výstupu PC 0 E 37/14 generována žádost o přerušení INTR B, která vygeneruje nulu na signálu DR, který vede do řadiče přerušení 3214. Přerušení zanikne, je-li programem přečten obsah portu PB, nebo li čtená data z disku.

- Při zápisu zapíše program data do portu PA, až je zápisový obvod nepotřebuje, vygeneruje signál ACK (děkuji) a ten nastaví na výstupu PC 3 (INTR/A) přerušení pro 3214. Program zapíše do portu další data k zápisu a přerušení zmizí.

- Časovač 8253 slouží jednak ke generování přenosové frekvence pro obvod UART 8251 a jednak pro doplňkové časování některých operací flopydisku.

- Čítač 0 časovače čítá frekvenci VS s periodou 20 ms a umožňuje tak počítači časovat některé operace.

- Čítač 1 čítá hodinky 1MHz a na vstupu G1 E 35/14 je spouštěn při operacích s diskem signálem SYN, který je odvozen od okamžiku zjištění značky. Časovač se používá pro časování okamžiku zápisu po zjištění značky. K tomu slouží klopný obvod LS 74 E 11/9 na jehož hodiny výstup časovače 1 vede. Na vstupu tohoto klopného obvodu je signál WRE (Write Enable) a hodiny pak vlastní zahájení zápisu zpozdí o přesnou dobu.

- Klopný obvod E14/8 hlídá časovou prodlevu náležící datové značky od signálu SYN, aby bylo zajištěno, že příslušná data patří jen k předešlé adresové značce.

Klopné obvody E 14/5 a E 11/5 pracují pouze při formátování a určují jednu celou otáčku disku pro funkci programu FORMÁT.

- časovač 2 obvodu 8253 E 35 slouží jako počítadlo přenesených bajtů z anebo do počítače. Čítají se vlastně změny signálu DR (Data Ready). Po přenesení noprogramovaného počtu bajtů vznikne signál OVFL (přečtení) a program pro obsluhu disku ví, že má ukončit přenos. Signál OVFL vznikne i při ukončení formátování, když se po druhé otáčce disku nastaví do jedničky klopný obvod E 11/5.

- Registr LS 174E 27 slouží jako registr příkazů, které určují, jaká operace bude prováděna. Jsou zde signály:

| RE | READ Enable |

| WRE | Write Enable |

| RDM | Read Data Mark |

| FOR | Formát |

- Posledním obvodem v řadiči flopydisku je paralelní obvod 8255 A E 34. Tento obvod slouží jako pro generování pomocných signálů jak pro řadič flopydisku tak pro ostatní obvody počítače.

- Jeho port B slouží jako generátor konstanty pro hardvérové rolování obrazovky ve spojení se sčítačkami na listu č. 3. Dva registry zařazené za portem PB 0 až PB 7 pouze synchronizují změnu konstanty se zobrazením s doběhem signálu RAS G.

- Port PA obsahuje některé výstupní bity, na které nikde jinde nezbylo. Jsou zde povolení přerušení pro myš a RTC a dva bity hodin C 3 a C 4 pro možnost záznamu adresové značky s chybějícími hodinami na flopydisku.

- Dále je zde jeden tranzistor pro libovolné použití jako jedno bitový port, např. pro servisové propojení dvou počítačů při tvorbě programů, nebo při oživování počítače.

- Dále jsou zde řídící signály pro mechaniku flopydisku:

| STEP | krok o stopu |

| DIR | směr kroku dovnitř/ven |

| T 43 | stopa větší než 43 |

| HL | přiklopení hlavy disku |

| a signály vstupní z disku do řadiče | |

| TOO | nultá stopa |

| WP | ochrana zápisu na disketu |

| INDX | indexový impuls (používá se při formátování) |

| jsou zde uvedení další signály flopydisku z listu č. 7 jako | |

| WE | povolení zápisu |

| WD | data k zápisu |

| RD | čtená data |

| S 0 až 1 | dva signály výběru jednoho ze dvou disků |

- Tím by bylo možné ukončit popis funkce řadiče flopydisku

TRACK

| index gap | sector 1 | ... | sector n | track gap |

SECTOR

| sector identif. | identifier gap | data block | data gap |

SECTOR IDENTIFIER

| identifier mark | adress identifier | CRC |

DATA BLOCK

| data mark | data field | CRC |

OBR. 1. 9

Nutno poznamenat, že se jedná o formát používaný u disket s jednoduchou hustotou záznamu (tzv. FM záznam) při dvojnásobné hustotě záznamu (MFM záznam) je formát poněkud odlišný. Od formátu záznamu FM se liší především dvojnásobnou délkou mezer a datových polí. Je to způsobeno dvojnásobnou přenosovou rychlostí.

Nyní ale zpět k obr. 1.9, postupně se seznámíme s obsahem všech bloků.

INDEXOVÁ MEZERA (INDEX GAP)

Tato mezera začíná u indexového otvoru a její délka je 73 bajtů. Tato mezera téměř nemá žádný význam, lze ji používat pro odstartování čtení celé stopy. Pro zápis se nepoužívá. Z těchto důvodů je často, zvláště pak u „hustších" formátů, vynechávána.

IDENTIFIKAČNÍ MEZERA (IDENTIFIER GAP)

Tato mezera obsahuje při formátování 11 bajtů OFFH. Velikost identifikační mezery se v průběhu používání diskety mírně mění v důsledku přepisování datového pole diskety.

BLOKOVÁ DATOVÁ MEZERA (DATA BLOCK GAP)

Tato mezera odděluje datové pole od následujícího ID pole a je dlouhá 27 bajtů. Její délka se mění v průběhu používání diskety vlivem rozdílných rychlostí otáčení diskety v různých mechanikách a nepřesností při zápisu.

MEZERA ZA STOPOU (TRACK GAP)

Tato mezera slouží k oddělení posledního bloku dat od indexové mezery. Její délka závisí na tolerancích frekvence zápisu a otáček motoru. Zapisuje se při formátování za poslední sektor konec zápisu je určen příchodem indexového impulsu. Délka této mezery je obvykle 101 bajtů.

Identifikace počátku identifikačního a datového pole vyžaduje zvláštní bitové vzory, nutné pro synchronizaci vnitřních obvodů řadiče pružných disků. Tyto bitové vzory se nazývají adresové značky (AM). Lze je rozlišit pomocí chybějících hodinových impulsů (data mají vždy všechny hodinové impulsy, tj. že hodiny v datech jsou 0FFH).

Existují celkem čtyři různé adresové značky:

- INDEXOVÁ ADRESOVÁ ZNAČKA (INDEX - AM) uvnitř indexové mezery

- ID ADRESOVÁ ZNAČKA (ID - AM) na začátku ID pole

- ADRESOVÁ ZNAČKA DAT (DATA - AM) na začátku datového pole

- ADRESOVÁ ZNAČKA ZRUŠENÝCH DAT (DELETED DATA - AM) na začátku pole zrušených dat.

Vzhledem k tomu, že obvody, které tyto značky detekují nebo generují při zápisu, jsou součástí monolitických řadičů pružných disků, nepokládám za důležité se v dalším výkladu hlouběji zabývat jejich tvarem a zpracováním.

Skládá se z identifikační adresové značky (ID - AM), adresy a zabezpečovacích bitů CRC.

IDENTIFIKAČNÍ ZNAČKA (IDENTIFIER MARK)

Toto pole má délku 7 bajtů - 6 bajtů 00H sloužících k synchronizaci datového separátoru řadiče pružných disků, pak následuje ID adresová značka.

ADRESA (ADRESS IDENTIFIER) Adresa obsahuje těchto následujících 6 bajtů:

- ADRESA VÁLCE (CYLINDER ADRESS): obsahuje v binárním tvaru adresu válce (stopy) v rozsahu 0 až 76 (pro 8" disk).

- ADRESA STRANY (SIDE ADRESS): reprezentuje v binárním tvaru adresu strany (0 nebo 1)

- ADRESA SEKTORU (SECTOR ADRESS): určuje v binárním tvaru adresu sektoru v rozsahu 1 (první sektor) až max. počet sektorů na stopě.

- DÉLKA SEKTORU (SECTOR LENGTH): tento bajt určuje délku sektoru (00 H = 128 bajtů, 01 H = 256 bajtů, 02 H = 512 bajtů atd.)

- ZABEZPEČOVACÍ BITY CRC (CRC BYTES): tyto dva bajty

jsou generovány vnitřními obvody řadiče (16-ti bitový registr se zpětnými vazbami).

V datovém poli je uložena datová značka, datové pole a zabezpečovací bity CRC.

DATOVÁ ZNAČKA (DATA MARK)

V tomto poli se nachází 7 bajtů. Prvních 6 je obsazeno 00H a slouží k synchronizaci řadiče. Pak je zde datová adresová značka. Pokud při čtení tohoto pole narazí řadič na adresovou značku indikující pole zrušených dat (DELETED DATA AM), jsou data tohoto sektoru ignorována a řadič čte následující sektor. Musím ale poznamenat, že výše popsaného postupu se v praxi velmi málo používá. Většina operačních systémů si totiž vede samostatný přehled o obsazených sektorech disku (tzv. alokační vektor disku v systému CP/M).

DATOVÉ POLE (DATA FIELD)

Teprve až v tomto poli jsou uložena vlastní data (!). Zde je patrné o kolik je princip záznamu na pružný disk složitější než běžně používané systémy záznamu na magnetofonové kazety.

Formát stopy

Každá stopa je rozdělena na několik sektorů pro ukládání dat. Jsou to jakési „přihrádky". Každá taková přihrádka je označena záhlavím (ID field), ve kterém jsou zapsány informace o čísle sektoru, stopy atd. Pak teprve následuje pole pro uložení dat. Začátek každé stopy je jednoznačně určen pomocí indexového otvoru v disketě. Poloha tohoto otvoru je čtena optickým čidlem obdobně jako otvoru pro ochranu zápisu. Sektory jsou číslovány 1, 2,.. n, kde n = počet sektorů na stopě je zde tedy rozdíl od číslování stop (první stopa má číslo 0!).

Vytvoření sektorů - „přihrádek" a patřičných identifikačních záhlaví se nazývá „formátování diskety." Identifikační záhlaví sektorů slouží pro orientaci při zápisu nebo čtení dat z diskety, podle informace ze záhlaví vybírá řadič sektor, ke kterému požadujeme přístup. Při formátování je rovněž zaplněno datové pole sektoru (zpravidla bajty s obsahem 0E5H). Obsah záhlaví je při korektním (nehavarijním) přístupu na disketu neměnný, mění se pouze údaje v datovém poli. V případě narušení informací v záhlaví je nutné disketu znovu naformátovat, což zpravidla vede ke ztrátě údajů z datového pole. Použitelnou kapacitu diskety jednoduše vypočteme, jestli že vynásobíme počet stop x počet sektorů x délka sektoru. Takto vypočtená kapacita je poněkud menší, než-li „hrubá". - neformátovaná kapacita diskety, vzhledem k tomu, že značná část kapacity připadne na mezery mezi sektory.

Na následujícím obrázku si ukážeme, jak jsou jednotlivé sektory rozloženy na stopě a blíže se seznámíme se strukturou záhlaví sektoru (dále jen ID pole).

Autor textu: ing. Eduard Smutný, 1989

Náklad: 1000 ks výtisků

Vytiskla tiskárna St. st. Klíčany, SPV

Výkres osazení

Elektrické schéma

Elektrické schéma č. 1 PROCESOR

Elektrické schéma č. 2 PAMĚŤ

Elektrické schéma č. 3 VIDEO I

Elektrické schéma č. 4 VIDEO II

Elektrické schéma č. 5 PŘERUŠENÍ

Elektrické schéma č. 6 PORTY

Elektrické schéma č. 7 FLOPY I

Elektrické schéma č. 8 FLOPY II

Elektrické schéma č. 0

PROM (INTEHEX)

Přílohy:

Schéma FK-1 a černobílá verze ZDE.

Schéma č. 1 PROCESOR a černobílá verze ZDE.

Schéma č. 2 PAMĚŤ a černobílá verze ZDE.

Schéma č. 3 VIDEO I a černobílá verze ZDE.

Schéma č. 4 VIDEO II a černobílá verze ZDE.

Schéma č. 5 PŘERUŠENÍ a černobílá verze ZDE.

Schéma 6 PORTY a černobílá verze ZDE.

Schéma č. 7 FLOPY I a černobílá verze ZDE.

Schéma č. 8 FLOPY II a černobílá verze ZDE.

Schéma č. 0 a černobílá verze ZDE.

"ROM SEP" E6 PROM MH74S287

:020000040000FA :20000000F0F0F1F0F0F0F1F0F0F0F0F0F0F0F0F0F0F0F1F2F0F0F1F2F0F0F0F0F0F0F0F0D8 :20002000F0F0F0F3F0F0F0F3F0F0F0F0F0F0F0F0F0F4F0F0F0F4F0F0F0F0F0F0F0F0F0F0B2 :20004000F0F5F0F0F0F5F0F0F0F0F0F0F0F0F0F0F0F6F0F0F0F6F0F0F0F0F0F0F0F0F0F08A :20006000F0F0F0F7F0F0F9F0F0F0F0F0F0F0F0F0F0F0F0F8F0F0F0F0F0F0F0F0F0F0F0F068 :20008000F0F0FFF0F0F0F0F0F9F9F9F9F9F9F9F9F0F0F0F0F0F0FBFAFAFAFAFAFAFAFAFAA4 :2000A000F0F0F0F0F0F0F0FFFBFBFBFBFBFBFBFBF0F0F0F0F0F0FFF0FCFCFCFCFCFCFCFC6A :2000C000F0F0F0F0F0F0F0F0FDFDFDFDFDFDFDFDF0F0F0F0F0F0F0F0FEFEFEFEFEFEFEFE48 :2000E000F0F0F0F0F0F0F0F0FFFFFFFFFFFFFFFFF8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F808 :00000001FF

"ROM DEK" E46 PROM MH74188

:020000040000FA :20000000075F6F5F0D5F6F5F0B5F6F5F0D5F6F5F5F5F5F5F5F5F5F5F5F5F5F5F5F5F5F5F10 :00000001FF

"ROM VS" E98 MH74S571

:020000040000FA :20000000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFB80 :20002000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFB60 :20004000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFB40 :20006000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFB20 :20008000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFB00 :2000A000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBE0 :2000C000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBC0 :2000E000FBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBFBA0 :20010000F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F0F0F0F0F0F0F094 :20012000F0F1F1F1F1F1F1F1F1F1F1F1F1F1F1F3F3F3F3F3F3F3F3F3F7F7F7F7F7F7F7F75E :20014000F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7BF :20016000F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F79F :20018000F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F77F :2001A000F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F75F :2001C000F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F73F :2001E000F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F71F :00000001FF

"PRO HS" E117 MH74S571

:020000040000FA :20000000FAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAF8F8F8F8F8F8F8F8F8F8F8B6 :20002000F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8C0 :20004000F0F0F0F0F0F0F0F0F0F0F0F0F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F278 :20006000F2F2F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F3F322 :20008000FEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFCFCFCFCFCFCFCFCFCFCFCB6 :2000A000FCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCC0 :2000C000F4F4F4F4F4F4F4F4F4F4F4F4F2F2F2F2F2F2F2F6F6F6F6F6F6F6F6F6F6F6F6F694 :2000E000F6F6F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F7F722 :20010000FAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAFAF8F8F8F8F8F8F8F8F8F8F8B5 :20012000F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8F8BF :20014000F0F0F0F0F0F0F0F0F0F0F0F0F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F277 :20016000F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F2F23F :20018000FEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFEFCFCFCFCFCFCFCFCFCFCFCB5 :2001A000FCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCFCBF :2001C000F4F4F4F4F4F4F4F4F4F4F4F4F2F2F2F2F2F2F2F6F6F6F6F6F6F6F6F6F6F6F6F693 :2001E000F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F6F63F :00000001FF

E127 MH74188

:020000040000FA :200000002525242622022E2E2A6A2525252727272525242622022E2E2A6A1535B4B6B2B294 :00000001FF

BOOT EPROM (INTEHEX)

"BOOT EPROM" E65 MHB2716

:020000040000FA :20000000F33100002195001100FF011000EDB03EFFED47ED5E3EAED3033EA6D3233E88D357 :2000200063AFD361D350D3623E44D3603E0CD3033E04D303CD6E04CD6803F33E03D330FB8C :200040000E00CDB5000E00CDBA00210080061A0E01CD7600E50E01CDBA00E1061A0E01CD10 :200060007600F32171001110FF010500EDB0C310FFDB30C30080E5C5CDBF00444DCDC4004A :20008000CDC900B7200AC1E1118000190C10E7C9CD6803F376A500A500A500A500A500A552 :2000A00000A500A500F5DB70D3703E08D330F1FBED4DC38204793200FEC9793201FEC9795D :2000C0003202FEC9ED4303FEC9C3F6017E23B7C8E54FCDB200E118F4DDE5E5D5C5F5111F4B :2000E000FF211EFF3600010400EDB0EB36FBE5EB132A03FE018000EDB0D5DDE103E10681A5 :20010000CD4604DD7200DD7301DD3602FFF1C1D1E1DDE1C921AE012200FF211EFF11203594 :200120003E89D312AFD3123206FE3E02D3503E04D3233E0DD3230E20EDA3FB3A06FEB7209F :200140000B1B7AB320F5F33E813206FEF3FE0137C0AF3206FEC9D93E83D312AFD31232066D :20016000FE112035211EFF0E21AFD3503E05D350FB3A06FEB7200E1B7BB220F5F33E813217 :2001800006FE37D9C9F3FE0120F8211EFF0681CD46043E813206FE7ABE20E7237BBE20E20A :2001A0003E003206FEB7D9C90000D301E301087EEDA3E6032809D36011C601ED5300FF3E02 :2001C00003D33008FBC9F5EDA3AFD3603E03D330F1FBC9F53E023206FEAFD3503E03D3306C :2001E000F1FBC9F53EB0D3133E0118EAF5EDA23E03D330F1FBC9F3E5D5C5D9E5D5C5CDCA62 :2002000002060AC5210016CD06033021CDFA02C110F1373E4CD3603E04D3233E08D3303A6F :2002200006FECBBFC1D1E1D9C1D1E1FBC9CD5601C1380F211FFFED5B03FE018000EDB0B724 :2002400018D110BF18CCF3E5D5C5D9E5D5C5CDD800CDCA02DB62CB6F28073E023206FE18C6 :2002600011060AC5212002CD06033021CDFA02C110F1373E4CD3603E0CD3233E08D3303AEC :2002800006FECBBFC1D1E1D9C1D1E1FBC9CD1401C130E010CE18DBDDE5E5C5DD2110FF3E12 :2002A000FEDD77003A01FEDD7701AFDD7702DD77043A02FEDD77032110FF0605CD4604DD41 :2002C0007205DD7306C1E1DDE1C9E5F53A00FE3205FECD3D043A01FECD91033E72D3133E65 :2002E000B0D313DB62CB5FCC2704AF3209FE21EC012200FFCD9702F1E1C9F5CDC9033A0129 :20030000FECD9103F1C9D9112035D97DD3117CD3113E02320AFE3E06D312AFD312D92117A3 :20032000FF0E21AF3206FED360AF3209FED3503E05D3233E09D350FB3A06FEB7200E1B7B15 :20034000B220F5F3D93E813206FE37C9F3D9FE0120C42117FF1110FF0107001A13EDA1C28A :200360001603EA5B03B718E3E5D5C5F521A8011100FF010600EDB03EFF3207FE3208FEAF1D :20038000D3623205FE3E04D323CD3604F1C1D1E1C9C5F54FCDEF03382D9147281B3E02F20D :2003A000A9033CF578ED4447F1D3633E01D363AFD363CD17040810F379CD0604FE2B3E0441 :2003C00038013CD363B7F1C1C9C53E04D3630650DB62B7CB6720113E02D3633DD363AFD3EB :2003E00063CD17040810E9373E00D40604C1C93A05FEB73A07FE28033A08FEB7F0CDC903F6 :20040000D8AFCD0604C9F53A05FEB72805F13208FEC9F13207FEC9E3C5F546233EC83D2053 :20042000FD10F9F1C1E3C9F53E07D363CD17041EAF3209FEF1C9F53E06D363F1C9F5E6013B :20044000C60AD323F1C911FFFF7E23AA534F0F0F0F0FE60FA95F0F0F0F4FE61FAA5779E606 :20046000E0AB5F790FE6F0AA5710DEC90000F321004011014001FF3F3600EDB0AFD3613DA4 :20048000FBC9C900B201B9C28F033E02C39903FE04D2CF0BFE02CACF0B0E09C382050E02AD :2004A00021D60CCDFC00C2E003510C0C0CCD5601C2CF0BFE08DADD03DE08CDB501CD270178 :2004C000C2C5033E02FE07DAD503DE03CD20013E3382C32A04070D15CADD030E0BC3260310 :2004E0000E01219A0DCDFC00C24505CD9F01FE28CAB904CD4E01FE08D25B0457CDD600F6F3 :200500004047CD5601CA1604FE49C240047ACDCC010657C36504FE08D21F04B0C3F401DE21 :200520000BCD2701C233043E06B0CDF401CDBD00C3F401DE064F7ACDCC01790E0AC38205A8 :20054000FE28CA4D0478F606E63FC32A047ACDCC01163A3A0C0E4F7AC3A402FE49C26A046F :20056000CDC90106473EEDC39902CD7A0147CD2701C276040602CD5601C29404CD7A014F31 :2005800078FE03C2CF0B79FE02CA8F04CD20013EF9C3F401FE28CAA0044F780601C3A002CC :2005A0003A0C0E4F78FE02C2AF043E2AC3A4023EEDCDF4013E7BC3200ECD1C00CADF04FEAF :2005C00049CA0E05CD7F014FFE023E06CAFC03D2CF0B0602CD5601CDCC017948C38205CD02 :2005E000AA0ECD9F01FE41C2EF043E32C39302CD7F01FE02CAFD04CD2701C202053E22C321 :200600009302F53EEDCDF401F10643C38F02CD9F01FE580604CA1E05FE59C2CF0B0478CDDF :200620002001CDD00047CD5601CA3605573E36CDF40178C34A04FE06CACF0BFE08D2CF0B1C :20064000F670C399020E0121DE0CCDFC00C26105CDD0004FE607C2CF0B79E6F8F6C7C3F48B :20066000010E0221EA0CCDFC00C289050DC275050EC1C377050EC5CDBB01CD2701C2820548 :200680003E02CDDC00B1C3F4010E0221F20CCDFC00C2D2050D51CD1C00CAC505FE28CAB0FC :2006A00005D5CDE601D1F6C05F147A82B3C395027AB7C2CF0BCDB201FE02CAC005CD2001DF :2006C0003EE9C3F4014F7AB73EC3CAA4023ECDC3A40221F60CCDFA00C2F005CD8C0EFE0DC3 :2006E000CAEB05CDD201F6C0C3F4013EC9C3F4010E0221A60CCDFC00C24506CD5601CA11BB :20070000060DCACF0BCDBD0047CDC9013ED3C399025FCD5601CA25060DC2CF0B7BCDCC0115 :200720003EDBC32A04570DCA2D067B5A57FE13C2CF0B3EEDCDF4017BFE08D2CF0BCDB501D8 :200740000640C3260321FA0CCDFA00C2CF0BCD5601FE14C26806CD5601FE0ACA6306DE0832 :20076000CD20013EE3C3F401FE0ECA7206FE16C277063E08C3F401FE09C2CF0BCD5601FE4E :200780000AC2CF0B3EEBC3F4012A0E00D5EB2A0C007B957A9CD29D062A1300F9C9D17E2398 :2007A000220C00C932B00678E6DDFEDD3AB006C900CD55073CE607FE06DADA06CAD8067B58 :2007C000E6DFFEDDC2D106CD890632FC0BCD350AC90021F206C3A40EC603FE05DAE906C68D :2007E00002CDA406C2E906C601C6414FC31500484C0028484C290043CDB406FE40C80CFE87 :00000001FF

TEST EPROM (INTEHEX)

"TEST EPROM" E65 MHB2716

:020000040000FA :20000000F3ED5EDB5026020E00FD212500DD21190016011EFF06FFDDE9ED7810FA1D20F547 :200020001520F0FDE9FD2131001601DD211B0018E22520D3AFD361FD211F061112060E00C7 :20004000FD6605FD6E04DD214C0079E9FD66002E00DD210000DD19DD7E00FEFF2006DD211C :20006000120618F3CB41201977DD237CFDBE0128032318E37DFEFF20F8CB412012CBC118AC :20008000BF7EDDBE0028E2EBFD6603FD6E02E9131AFEFF20A918F1CA1E01FD21AE00D9212C :2000A0000040360011014001FF3FEDB0FDE9211501D9210040FD21BB001829DD7E00FD21B2 :2000C000C700210061181D2178407AFD21D10018132178617BFD21DB001809D9E9FD214E78 :2000E0000221645206080E5136FF2436FF1809CB7F20F5368024360125230D20F236FF24DB :2001000036FF087DD6516F24243E05B8200124080710D3FDE9FD2134001614C32B00FD21A7 :200120002501C39F00111E40D9FD212506C33B00D94F2143013EFF12141214121412151530 :200140001513E90619215501CB4120E93E801214143E0118E710EE215C0118D97BD61B5F75 :20016000CB412003D9DDE97AC6055718F72814FD217601C39E00217C01C3B100FD211E0185 :20018000C31901210000110080014106EDB00E0016800605312B06DDE1DD7E019182DD7759 :2001A0000110F4C3A681118040D9FD213586DB30C33B80DD21BE8108DB5008C33081DB304D :2001C000C34C8008DB5008C3CA01C26F01FD213B06C33B00CB472812D91619FD21E201C320 :2001E0002B00D9FD213B06C34C001AFE55CA4C003E88D3632100401640AF0E2006087723D2 :2002000010FC2F0D20F62F1520F0AF57DD211D02D3610E2006FF10FE0D20F9DDE93C20F05C :20022000BA200A14DD212A0218E63D18F1F331FEFEDD21F8053EFFED473E803212FF1813A0 :20024000DD2A10FFDD6601DD6E00AFBC28F2C9F3CDDD0208CD4402DD2210FFF1E52B2BE5D2 :20026000FD216702C39F0011145B218005CDD102CDD10214DDE1DD7E00CDC502DD7E01CD45 :20028000C50221D4051100FF011000EDB00605AF00D34110FAD3613EAED3033E05D3033EBA :2002A00088D3633E48D3603E90D313D312F53EA6D323F1F5D3703E08D330F1FBED4DDD23C7 :2002C000DD23C1188E26006F070707956F018E0509010700EDB07B1E07935F14C9CD400249 :2002E000DB01FEF228D8FE7F28D4FEF7C0DD2BDD2B18CF0000F31100FF21E405011000ED02 :20030000B01600FB18FEF314F314F314F3141803F3DB7014F314F314F37ACDDD00CD850303 :200320001600FE01CCDD02C38D020001082FCDDD0018FE00023A12FF073212FFCDDD00D39F :200340000018FE0003015C03CD5203060116FFFB18FEF3ED4306FF3E04D360C9F305C2AD08 :2003600002147ACDDD00063318F20004F3017C03ED4308FFFBDB70CDDD0018F9F3CD850309 :20038000DB70C3AD02E5C5F521125A0E07060B7E2F772C10FA7DD60B6F240D20F0F1C1E153 :2003A000C900053E44D3603E34D3133E32D310AFD3103E74D3133EFFD311D31118FE0006C4 :2003C000AFD3603A12FFE60F20023E80073212FFD350C32E0300073E76D3133EFED3113CBD :2003E000D3113E40D3413E3C00D3413E5500D3410000D341F3010504ED430AFF3E553E3304 :20040000D341FB18FE3E55D340C3AD020008F3CD1504FB18FE015904ED4300FF010E04CD40 :2004200027043E02D350C9ED4302FFED4304FFAFD3603E72D3133E32D311AFD3113EB0D3E1 :20044000133EFFD3123EFFD3123E40D360AFD3603E0DD3233E55D320C9F3CD3D04CD22042E :20046000CDB60200092E003E0AD323CD77043E0BD323CD770418F0CDAA04DB62CB6F3EFE7D :20048000C4C20420F5060F160326000E057CCDC2047AD362241E50CDD3041D20FA0D20ED11 :2004A0007AEE085710E5CDAA04C9065016017AD362CDCC04DB62CB67C010F33EFFCDC20481 :2004C00018E8C5F5E5CDDD00E1F1C1C9D51E64CDE004D1D57AEE01D3621EFFCDE004D1C9C3 :2004E000DB62CB7F200ACB452802CB851D20F1C9CB4520F8CBC5CD850318F10100F3012798 :2005000005ED4300FF01FD04CD2704CD13050619FB18FE3E55D3203E11D350013305ED4337 :2005200006FF3E04D360C9F3DB21CD3D04CD1305CDB602F305C2B3023E08D362061410FEFF :20054000AFD362061A18EC010121FF7F0E000640CD790577253E6E3D20FD10F4267F2D0DCE :2005600020ECCD790532004021FE7F11FF7F01FF3FEDB8066410FE18E9DB11FE0028FAC953 :200580003C42403C02423C3C4242424A463E3C42424A52423C081828480808083C4202040B :2005A00008103E3E42040C02423C102040447E04047C40407C02423C3C42405C62423C7E2B :2005C0000202040810203C42423C42423C3C42463A02423CAD02AD02AD02AD02AD02AD0287 :2005E0004F02AD02060308030A030C0310031403160318030000F001F5022C0335034503D6 :200600006C03A303C003D7030E046504FD044905000055FEAA0155FEAA0155FEAA01FF4025 :200620007F97004C0080FF6D0130013C806080338146815881007FC381B38140FF6F01D4D0 :200640000102040810203C42423C42423C3C42463A02423CAD02AD02AD02AD02AD02AD0207 :200660004F02AD02060308030A030C0310031403160318030000F001F5022C033503450355 :2006800000000000000000000000000000000000000000000000000000000000000000005A :2006A000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF5A :2006C000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF3A :2006E000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF1A :20070000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF9 :20072000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFD9 :20074000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFB9 :20076000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF99 :20078000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF79 :2007A000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF59 :2007C000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF39 :2007E000FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF19 :00000001FF

Dokumentace ke stažení

Oskenovaný technický popis (JPG) ke stažení ZDE 13MB.

Oskenovaný technický popis (PDF) ke stažení ZDE 17MB.

Oskenovaná schémata (JPG) ke stažení ZDE 5MB.

Oskenovaná vyčištěná schémata (PNG) ke stažení ZDE 4MB.

Překreslené schémata (PDF) a obsahy xROM (INTELHEX) ke stažení ZDE 1MB

Technický popis počítače FK-1

- Stručná charakteristika počítače

- Pravidla používaná při popisu schémat

- Popis listu č. 1 PROCESOR

- Popis listu č. 2 PAMĚŤ

- Popis listu č. 3 VIDEO I

- Popis listu č. 4 VIDEO II

- Popis listu č. 5 PŘERUŠENÍ

- Popis listu č. 6 PORTY

- Popis listu č. 7 FLOPY I

- Popis listu č. 8 FLOPY II

- Výkres osazení

- Elektrické schéma

- Elektrické schéma č. 1 PROCESOR

- Elektrické schéma č. 2 PAMĚŤ

- Elektrické schéma č. 3 VIDEO I

- Elektrické schéma č. 4 VIDEO II

- Elektrické schéma č. 5 PŘERUŠENÍ

- Elektrické schéma č. 6 PORTY

- Elektrické schéma č. 7 FLOPY I

- Elektrické schéma č. 8 FLOPY II

- Elektrické schéma č. 0

- PROM

- BOOT EPROM

- TEST EPROM

- Dokumentace ke stažení