OCR návodu UDR-1

SAPI-1 6XV 122 56 UDR-1

UNIVERZÁLNÍ DESKA ŘÍZENÍ

6XK 199 74

TESLA ELSTROJ * TESLA LIBEREC * TESLA ELTOS-DIZ

Obsah:

- Úvod

- Technické parametry

- Popis funkce

- Programováni

- Instalace

- Testováni

- Údržba a servis

- Všeobecné údaje

Přílohy:

Závady:

Úvod

- obvod 8255, kterým prochází 8 vstupů s úrovněmi TTL. Čtyři z těchto vstupů jsou zapojeny do systému přerušeni.

- tento obvod 8255 zajišťuje 8 výstupů /max. 24V/100mA/ pro spínáni žárovek, relé nebo různých akčních členů /ventily, krokové motorky atd./

- obvod 8253, který lze zapojit jako hodiny reálného času /ve spolupráci s přerušovacím systémem/ nebo jako čítač, generátor frekvence apod.

- druhý obvod 8253, pomoci něhož jsou realizovány dva D/A převodníky pracující na principu šířkové modulace a následné integrace. Převodníky maji přesnost 8 bit a jsou vhodné pro regulaci nebo pro liniové zapisovače apod.

- přerušovací systém je plně ovladatelný /povolení přerušeni, identifikace zdroje přerušeni, nulováni žádosti o přerušení/

TECKICKÉ PARAMETRY

POPIS FUNKCE

Dekodér adresy

Zesilovače

Digitální vstupy

Digitální výstupy

Časovač a čítač /obvod 8253 - D3B/

Port PC obvodu 8255

D/A převodníky

PROGRAMOVÁNÍ

Příklad programu pro řízení D/A převodníků

Programováni portů 8255

Programováni čítače D3B 8253

INSTALACE

- Desku UDR-1 vyjmeme z obalu a překontrolujeme, zda při přepravě nedošlo k mechanickému poškozeni desky, zejména k poškozeni kontaktů FRB konektorů a přepínačů DIL.

- Pomoci přepínače S2 nastavíme adresový prostor desky /viz tab. 1/.

- Pomoci přepínače S1 nastavíme hodiny čítače 2 obvodu D3B /viz tab. 2/.

- Překontrolujeme, zda deska UDR-1 nezpůsobí překročeni max. proudového odběru napájecích zdrojů systému nebo překročeni povolené zátěže sběrnice.

- Desku UDR-1 zasuneme do jednotky JZS-1 /JZS-1A/ nebo do jednotky JPN-1 souboru SAPI-1. Desku je možné zasouvat nebo vysouvat jen při vypnutém systému!

- Připojeni periférii na vstupy In / výstupy Vn - konektor X2

- Zkontrolujeme, zda připojená zařízení splňuji požadavek ochrany zvýšenou izolaci min. 2,5 kV dle ČSN 36 9060.

- Obal desky uložíme pro potřebu zaslání desky do opravy.

TESTOVÁNÍ

ÚDRŽBA A SERVIS

VŠEOBECNÉ ÚDAJE

- Pracovní podmínky

- Krytí dle ČSN 33 0330 IP 00

- Deska je napájena ze zdroje, který odpovídá ČSN 36 9060

- Kvalifikace obsluhy a údržby: pracovník poučený dle §4 vyhlášky 50/78 Sb.

- Skladování

- Záruka

Univerzální deska řízení UDR-1 je vhodná pro malé aplikace systému SAPI-1 Je adresovaná jako vstup/výstupní zařízeni. Obsahuje tyto funkční bloky:

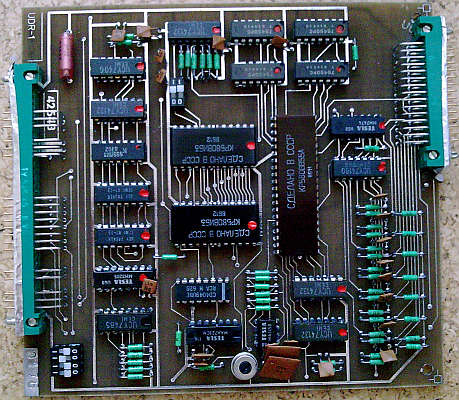

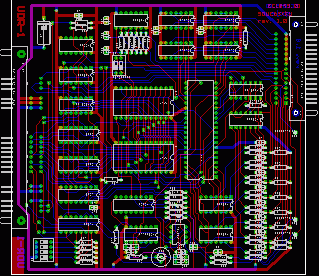

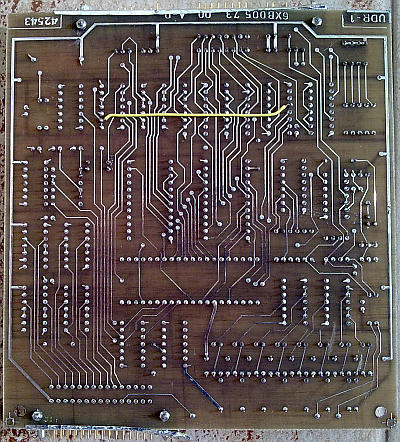

Desku UDR-1 tvoř osazoná deska plodného spoje o rozborech 140 x 150 mm. Pomoci 62-pólového FRB konektoru se deska UDR-1 připojuje na sběrnici ARB-1 /jednotka JZS-1, JZS-1A/ nebo na sběrnici IOB-1 /jednotka JPN-1/, 30-pólový FRB konektor je určen pro připojeni periférií.

| Napájecí napětí | + 5 V ± 0,25 V | |

| + 12 V ± 0,5 V | ||

| - 12 V ± 0,5 V | ||

| Odběr proudu | ze zdroje +5V | typ. 0,7 A max. 1 A |

| ze zdroje +12V | typ. 7 mA max. 15 mA | |

| ze zdroje -12V | typ. 5 mA max. 10 mA | |

| Vstupy I0 až I7 | úroveň TTL | |

| Výstupy V0 až V7 | zatižitelné do 24 V/100 mA max. | |

| Vstup IN PC3 | úroveň TTL | |

| Vstup IN CLK | úroveň TTL | |

| Výstup OUT2 | úroveň TTL | |

| Převodník D/A | - rozsah výstupních napětí | 0,02 V až 5 V v 255 krocích |

| - chyba převodu | max. 50 mV | |

| - dobo ustáleni převodníku | max. 0,1 s | |

| - výstupní odpor převodníku | cca 100 Ω | |

| Deska je adresovatelná jako I/O zařízeni – zabírá 12 adres | ||

| Rozměry desky PS | 140 x 150 mm | |

| Hmotnost | cca 130 g | |

Dekodér adresy umožňuje zvolit jednu ze 16 adres pomoci čtyřbitového přepínače S2. Adresy A7, A6, A5 a A4 ze sběrnice jsou porovnávány v komparátoru D7A /7485/ se stavem nastaveným pomoci přepínače volby adresy S2 - viz tab. 1.

Bity A1 a A0 slouží pro adresaci vnitřních registrů obvodu 8255 a obou obvodů 8253.

Bity A3 a A2 volí, zda je adresován obvod 8255 /A3 = A2 = 0/ nebo obvod 8253 /D2B/ pracující jako D/A převodník /A3 = 0, A2 =1/ a nebo obvod 8253 /D3B/ pracující jako čítač a časovač /A3 = 1 / A2 = 0 /. Bitová kombinace A3 = 1 a A2 = 1 není na desce využita, a proto jsou blokovány výběry /CS obvodů D4A a D5A hradlem D2A/1 připojeným na D6A/12.

Výstup komparátoru D7A/6 oznámí úrovni log. "1" na výstupu A ≡ B, že na sběrnici je adresa navolená na desce UDR-1. Tento signál povolí vstup dekodéru adresových bitů A2, A3 /obvod 3205 D6A - vstup E3/ a současně přes hradlo 74132 D2A/3 povolí /CS zesilovačů dat - 3216 D4A a D5A.

| PORTY 8255 D3C | ||||||||||||||||

| 00 | 10 | 20 | 30 | 40 | 50 | 60 | 70 | 80 | 90 | A0 | B0 | C0 | D0 | E0 | F0 | R/- port A |

| 01 | 11 | 21 | 31 | 41 | 51 | 61 | 71 | 81 | 91 | A1 | B1 | C1 | D1 | E1 | F1 | -/W port B |

| 02 | 12 | 22 | 32 | 42 | 52 | 62 | 72 | 82 | 92 | A2 | B2 | C2 | D2 | E2 | F2 | R/W port C |

| 03 | 13 | 23 | 33 | 43 | 53 | 63 | 73 | 83 | 93 | A3 | B3 | C3 | D3 | E3 | F3 | -/W řídicí slovo |

| ČÍTAČE PRO ŘÍZENÍ D/A PŘEVODNÍKU 8253 D2B | ||||||||||||||||

| 04 | 14 | 24 | 34 | 44 | 54 | 64 | 74 | 84 | 94 | A4 | B4 | C4 | D4 | E4 | F4 | R/W čítač 0 |

| 05 | 15 | 25 | 35 | 45 | 55 | 65 | 75 | 85 | 95 | A5 | B5 | C5 | D5 | E5 | F5 | R/W čítač 1 (převodník AN1) |

| 06 | 16 | 26 | 36 | 46 | 56 | 66 | 76 | 86 | 96 | A6 | B6 | C6 | D6 | E6 | F6 | R/W čítač 2 (převodník AN2) |

| 07 | 17 | 27 | 37 | 47 | 57 | 67 | 77 | 87 | 97 | A7 | B7 | C7 | D7 | E7 | F7 | -/W řídicí slovo |

| ČÍTAČE PRO OBECNÉ UŽITÍ 8253 D3B | ||||||||||||||||

| 08 | 18 | 28 | 38 | 48 | 58 | 68 | 78 | 88 | 98 | A8 | B8 | C8 | D8 | E8 | F8 | R/W čítač 0 |

| 09 | 19 | 29 | 39 | 49 | 59 | 69 | 79 | 89 | 99 | A9 | B9 | C9 | D9 | E9 | F9 | R/W čítač 1 |

| 0A | 1A | 2A | 3A | 4A | 5A | 6A | 7A | 8A | 9A | AA | BA | CA | DA | EA | FA | R/W čítač 2 |

| 0B | 1B | 2B | 3B | 4B | 5B | 6B | 7B | 8B | 9B | AB | BB | CB | DB | EB | FB | -/W řídicí slovo |

| X | X | X | X | X | X | X | X | nastavení spínače S2/1 [ X ] spínač sepnut | ||||||||

| X | X | X | X | X | X | X | X | nastavení spínače S2/2 [ ] spínač rozepnut | ||||||||

| X | X | X | X | X | X | X | X | nastavení spínače S2/3 | ||||||||

| X | X | X | X | X | X | X | X | nastavení spínače S2/4 | ||||||||

Tab. 1.: Adresace desky UDR-1

Obvod D3A pracuje jako zesilovač a oddělovač pro signály A0 , A1 , IOR a IOW

Obvody D4A a D5A /3216/ pracuji jako obousměrné zesilovače dat. Směr přenosu je řízen signálem IOR.

Hradlo D2A/8 zesiluje signál Φ2 - hodiny.

Hradlo D1A - 7406 /výstup s otevřeným kolektorem/ zesiluje signál INT0 - žádost o přerušeni.

Vstupní signály I0 až I7 přicházejí z konektoru X2 přes filtrační obvody a tvarovače D4C a D5C /74132/ na vstupy PA0 až PA7 obvodu 8255. Port PA tohoto obvodu pracuje v módu 0 ve vstupním režimu. Vstupy jsou přizpůsobeny pro spínací kontakt proti zemi /tlačítko, koncový mikrospínač, kontakt relé atd./ nebo pro úroveň 0V / + 5V. Sepnutý kontakt nebo log."0" na vstupech In se přečte do mikropočítače jako "1". Vstupy tedy platí v negativní logice. Vstupní filtr na každém vstupu zabraňuje pronikáni rušeni do vstupních obvodů, není však určen pro filtraci zakmitáváni kontaktů, neboť má malou časovou konstantu. Čtyři vstupy I4 až I7 jdou paralelně přes "detektor změny", který reaguje na jakoukoliv změnu /1 → 0 nebo 0 → 1/ kteréhokoliv z těchto signálů. V případě, že je povoleno přerušení /výstup PC4 = 1/ nastaví se klopný obvod do stavu D3D/5 = 0 při změně na vstupech I4 až I7 do jedničky a vznikne žádost o přerušeni //INT0 = 0/. Stav klopného obvodu žádosti o přerušení je možno přečíst v bitu PC0.

Port PB obvodu 8255 pracuje jako výstupní v módu 0. Výstupy PB0 až PB7 jsou zesíleny přes zesilovače 75450 PC. Tyto zesilovače na rozdíl od vstupů desky UDR-1 neinvertuji. Úrovni 0 na výstupu 8255 odpovídá sepnutý výstupní tranzistor v obvodu 75450 PC a to odpovídá log. "0" na výstupu.

Výstupy jsou zatížitelné až do 24V / 100mA, ale je nutné dbát na to, aby země výstupů X2/23, 25, 27, 29 byty zapojeny tak, aby se zemnící proud neuzavíral přes logické země systému. Výstupy je nutné při indukční zátěži chránit diodou:

obrázekObvod 8253 obsahuje 3 samostatné 16 bitové čítače. Každý čítač má vstup hodin, hradlovací vstup G a výstup. Každý čítač může pracovat v jednom z šesti druhů provozu.

Čítač 0 je na desce UDR-1 /D3B/ zapojen jako dělič vstupní frekvence 2 MHz /Φ2/, Jeho výstup je veden do vstupu čítače 1. Čítač 1 pracuje jako prostý čítač /v modu 0/ nebo dělič /mód 2 a 3/ a jeho výstup je zapojen na přerušovací systém desky, Změní-li se výstup čítače 1 z "0" na "1" nastaví se klopný obvod přerušení D3B/8 = 1 /pouze je-li přerušeni povoleno PC5 = 1/. Pomoci čítače 0 a 1 je tedy možné realizovat hodiny reálného času - to znamená periodické přerušování.

Čítač 2 má vstup hodin vyveden na přepínač S1, Při sepnuti S1/1 a rozepnuti S1/2 jsou hodiny 2 MHz a čítač 2 je v tomto případe možno použit jako generátor frekvence /výstup OUT2 na X2/10/. Při sepnutí S1/2 a rozepnuti S1/1 je vstup hodin externí /vstup IN CLK X2/12/ a je nožné použít jako čítač impulsů, řízený dělič frekvence atd. Hradlovací vstup čítače 2 je ovládán výstupem PC6 obvodu 8255.

| hodiny čítače 2 obvodu D3B | S1/1 | S1/2 |

| 2 MHz | sepnuto | rozepnuto |

| externí | rozepnuto | sepnuto |

Tab. 2.: Nastavení přepínače S1

Pozn.: Přepínač S1 nesmi být nastaven na jinou kombinaci než je uvedena v tabulce

Port PC pracuje v modu 0 - spodní čtyři bity PC3, PC2, PC1 a PC0 pracuji jako vstupy a horní bity PC7, PC6, PC5, PC4 jako výstupy.

Význam bitů.portu PC /obvod D3C/:

| PC0 | \ | přerušeni od změny vstupů I4 až I7 |

| PC1 | | | přerušeni od čítače 1 - hodiny reálného času |

| PC2 | } vstupy | čteni výstupu čítače 2 /obvod D3B/ |

| PC3 | / | externí vstup IN PC3 - X2/14 |

| PC4 | \ | povolení přerušeni od vstupů I4 až I7 |

| PC5 | | | povoleni přerušeni od čít. 1 - hod. reál. času |

| PC6 | } vstupy | hradlovací vstup čítače 2 |

| PC7 | / | hradlovací vstup čítače D/A převodníků |

Dva D/A převodníky pracují na principu šířkové modulace konstantní frekvence. Konstantní frekvenci vyrábí čítač 0 obvodu 8253/D2B/ pracující v módu 2 a jeho výstup spoušti dva monostabilní obvody /čítače 1 a 2 pracující v módu 1/. Volbou šířky výstupního impulsu danou naplněním čítačů 1 a 2 se na výstupech OUT1 a OUT2 dostane průběh s konstantní frekvenci a šířkou impulsu odpovídající zadaným číslům do čítaje 1 a 2. Tyto impulsy se vedou na přesné úrovňové spínače /CMOS obvod MHB 4049 - D4B/ a na integrační členy R29/C11 a R32/C20 a na zesilovače D6D/7 a D6B/1.

Referenční zdroj MAA 723 CN /D5B/ umožňuje nastavit výstupní úroveň napětí na + 5V při plné hodnotě vstupních čísel do čítače 1 a 2.

Inicializace D/A převodníku

MVI A, 91H ; řídící slovo pro 8255 do A OUT F3H ; zápis řídícího slova do 8255 MVI A,34H ; řídící slovo pro 8253 čítač 0 do A OUT F7H ; zápis řídícího slova 8253 MVI A,52H ; řídící slovo pro 8253 čítač 1 do A OUT F7H ; zápis řídícího slova do 8253 MVI A,92H ; řídící slovo pro 8253 čítač 2 do A OUT F7H ; zápis řídícího slova do 8253 MI A,0H ; nižší slabika pro čítač 0 do A OUT F4H ; zápis nižší slabiky do čítače 0 MVI A, 1H ; vyšší slabika pro čítač 0 do A OUT F4H ; zápis vyšší slabiky do čítače 0 MVI A,0FH ; spouštěcí slovo pro čítače do A OUT F3H ; zápis spouštěcího slova pro čítače do 8255

Start převodníku

CALL ARG1 ; získání argumentu ARG1 pro převodník AN1 do A OUT F5H ; spuštění převodníku AN1 CALI ARG2 ; získání argumentu ARG2 pro převodník AN2 do A OUT F6H ; spuštění převodníku AU2

Výstupní napětí D/A převodníků je určeno následující rovnici:

ARG

Uvýst = ----- , kde

51

| Uvýst | Požadované výstupní napětí převodníku |

| ARG | je konstanta /argument/ nabývající hodnoty od 1 do 255 |

Obvod 8255 je zapojen tak, že pro jeho funkční režim připadá v úvahu pouze mód 0 - port PA vstup, port PB výstup, bity PC0 až PC3 vstup a bity PC4 až PC7 výstup. Tím je jednoznačné dáno řídicí slovo 91H.

Čítač D3B 8253 má univerzální použití, proto zde neuvádíme příklad programování.

-

- zkontrolovat, zda není překročena zatížitelnost výstupů V0 až V7 /max. 24 V / 100 mA/.

- zkontrolovat, zda signály přivedené na vstupy I0 až I7 jsou v úrovních TTL.

Univerzální deska řízení UDR-1 je ve výrobním podniku testována testem TSX 18 v konfiguraci SAPI-1M

Údržba desky spočívá v udržováni kontaktů FRB konektorů. Tyto kontakty je nutno chránit před znečištěním a mechanickým poškozením, aby byla zajištěna spolehlivá činnost systému. Před každým zasunutím desky do sběrnice systému je nutno zkontrolovat, zda nejsou kontakty konektorů ohnuty, aby nedošlo k jejich ulomeni. Zvláštní pozornost je rovněž třeba věnovat přepínačům DIL, je nutno chránit je před znečištěním a mechanickým poškozením.

Servis desky UDR-1 zajišťuje dodavatel systému Tesla DIZ prostřednictvím svých servisních středisek, v případě odeslání desky do opravy je nutno ji zahalit do původního přepravního obalu.

| Teplota okolí | + 5°C až + 40°C |

| Relativní vlhkost | 40% až 80% při 30°C |

| Prostředí | neklimatizované, bez agresivních plynů a par |

| Atmosférický tlak | 84 až 107 kPa |

| Prašnost prostředí | max. 1 mg/m3 |

| velikost částic max. 10 µm | |

| Odolnost proti vibracím | 0,1 mm při 25 Hz |

Skladovací prostor musí být suchý, dobře větraný, bez mechanických otřesů a chemických vlivů. Skladovací teplota musí být v rozmezí - 5°C až + 35°C a relativní vlhkost vzduchu smí být max. 75%. Výrobky musí být skladovaný v neporušeném obalu. Při vybalováni desky /zvláště v zimním období/ je nutné ponechat výrobek v přepravním obalu 4 až 5 hodin v pracovních podmínkách, aby se zabránilo oroseni desky.

Výrobce ručí za jakost výrobku po dobu 6 měsíců ode dne splněni dodávky za předpokladu, že deska nebyla poškozena hrubým nebo neodborným zásahem.

Příloha: Tabulka konektoru X1

Příloha: Tabulka konektoru X2

Příloha: Rozpiska součastí

Příloha: Výkres osazeni UDR-1

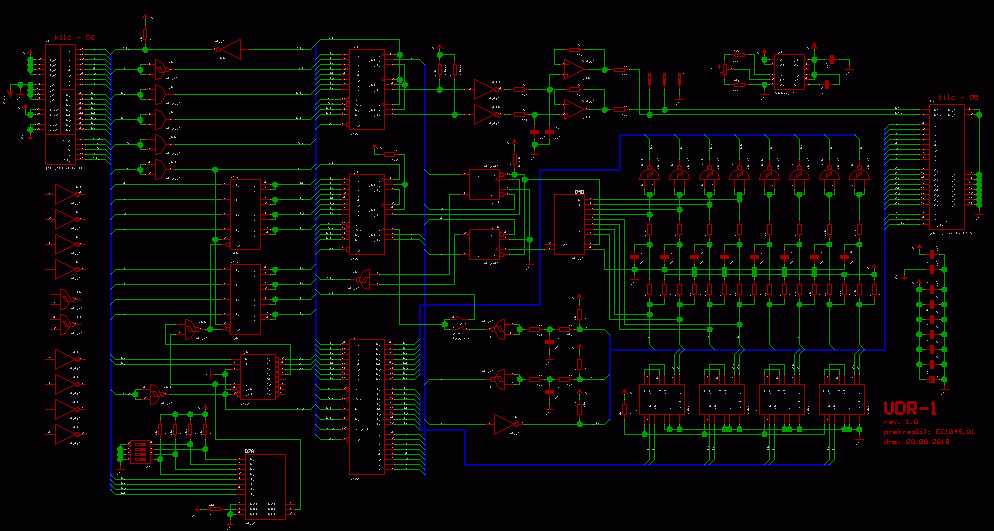

Příloha: Elektrické schéma

| Deska: UDR-1 Konektor: X1 Klíč: C6 Typ: TY 517 6211 | |

| Protikus: | Sběrnice ARB-1 /jednotka JZS-1, JZS-1A/ poz. X2 až X8 |

| Sběrnice IOB-1 /jednotka JPN-1/ pozice X1 až X8 | |

| č. | signál | význam | typ | č. | signál | význam | typ | |

| 1 | 2 | |||||||

| 3 | 4 | |||||||

| 5 | 6 | |||||||

| 7 | 8 | RES | RESET | INP | ||||

| 9 | 10 | IOR | čtení z portu | INP | ||||

| 11 | 12 | IOW | zápis do portu | INP | ||||

| 13 | 14 | |||||||

| 15 | +5 V | napájení | NAP | 16 | +5 V | napájení | NAP | |

| 17 | +5 V | napájení | NAP | 18 | +5 V | napájení | NAP | |

| 19 | 0 V | zem | NAP | 20 | 0 V | zem | NAP | |

| 21 | 22 | |||||||

| 23 | 24 | |||||||

| 25 | 26 | |||||||

| 27 | 28 | |||||||

| 29 | 30 | |||||||

| 31 | D4 | data | I/O | 32 | D3 | data | I/O | |

| 33 | D6 | data | I/O | 34 | D5 | data | I/O | |

| 35 | D2 | data | I/O | 36 | D7 | data | I/O | |

| 37 | D0 | data | I/O | 38 | D1 | data | I/O | |

| 39 | A1 | adresa | INP | 40 | A0 | adresa | INP | |

| 41 | A3 | adresa | INP | 42 | A2 | adresa | INP | |

| 43 | A5 | adresa | INP | 44 | A4 | adresa | INP | |

| 45 | A7 | adresa | INP | 46 | A6 | adresa | INP | |

| 47 | 48 | |||||||

| 49 | 50 | |||||||

| 51 | +12 V | napájení | NAP | 52 | +12 V | napájení | NAP | |

| 53 | 0 V | zem | NAP | 54 | 0 V | zem | NAP | |

| 55 | 56 | |||||||

| 57 | -12 V | napájení | NAP | 58 | -12 V | napájení | NAP | |

| 59 | 60 | Φ2 | hodiny Φ2 | INP | ||||

| 61 | 62 | INT0 | žádost o přeruš. | OUT |

| Typ signálu: | INP | vstupní |

| OUT | výstupní | |

| I/O | obousměrný | |

| NAP | napájeni |

| Deska: UDR-1 konektor: X2 Klíč: D5 | Typ: TY 513 3011 |

| Protikus: FRB zasuvka - 30-pólová | Typ: TX 514 3013 |

| č. | signál | význam | typ | č. | signál | význam | typ | |

| 1 | I4 | vstupní signál | INP | 2 | I6 | vstupní signál | INP | |

| 3 | I2 | vstupní signál | INP | 4 | I0 | vstupní signál | INP | |

| 5 | I1 | vstupní signál | INP | 6 | I5 | vstupní signál | INP | |

| 7 | I7 | vstupní signál | INP | 8 | I3 | vstupní signál | INP | |

| 9 | A zem | analogová zem | NAP | 10 | OUT2 | výstup čítače 2 | OUT | |

| 11 | AN1 | výstup D/A 1 | OUT | 12 | IN CLK | vstup ext. hodin | INP | |

| 13 | AN2 | výstup D/A 2 | OUT | 14 | IN PC3 | vstup portu PC | INP | |

| 15 | A zem | analogová zem | NAP | 16 | V0 | výstupní signál | OUT | |

| 17 | 0V | zem výst. signálů | NAP | 18 | V3 | výstupní signál | OUT | |

| 19 | 0V | zem výst. signálů | NAP | 20 | V1 | výstupní signál | OUT | |

| 21 | 0V | zem výst. signálů | NAP | 22 | V4 | výstupní signál | OUT | |

| 23 | 0V | zem výst. signálů | NAP | 24 | V2 | výstupní signál | OUT | |

| 25 | 0V | zem výst. signálů | NAP | 26 | V6 | výstupní signál | OUT | |

| 27 | 0V | zem výst. signálů | NAP | 28 | V7 | výstupní signál | OUT | |

| 29 | 0V | zem výst. signálů | NAP | 30 | V5 | výstupní signál | OUT |

| Typ signálu: | INP | vstupní |

| OUT | výstupní | |

| NAP | napájeni |

| ks | označení součásti | označení polohy | název |

| Konstrukční materiál | |||

| 1 | 6XB 005 73 | deska PS dvoustranná | |

| 1 | TY 517 6211 | X1 | vidlice FRB 62-pólová |

| 1 | TY 513 3011 | X2 | vidlice FRB 30-pólová |

| 1 | TS 501 2121 | S1 | přepínač DIL /2 přepínače/ |

| 1 | TS 501 4141 | S2 | přepínač DIL /4 přepínače/ |

| Pasivní prvky | |||

| 22 | TP 191 100RK | R2,R3,R5,R6,R8,R9,R11,R12,R14, | |

| R15,R17,R18,R20,R21,R23,R24, | |||

| R27,R30,R36,R37,R39,R40 | |||

| 1 | TR 191 680RK | R50 | |

| 19 | TR 191 1K0K | R1,R4,R7,R10,R13,R16,R19,R22, | odpor 0.25 W |

| R25,R26,R35,R38,R4l,R42,R44, | tolerance 10% | ||

| R45,R46,R47,R48 | |||

| 1 | TR 191 2K2K | R49 | |

| 2 | TR 191 4K7K | R33,R34 | |

| 1 | TR 191 47KK | R43 | |

| 4 | TR 191 100KK | R28,R29,R31,R32 | |

| 1 | TP 095 680RN | RP1 | odpor regulační |

| 1 | TE 981 20µ-PVC | C22 | kondenzátor elektrolytický |

| 7 | TK 783 15n | C12-C18 | kondenzátor keramický |

| 12 | TK 783 22n | C1-C8,C10,C19, | kondenzátor keramický |

| C21,C23 | |||

| 2 | TK 783 100n | C11,C20 | kondenzátor keramický |

| 1 | TK 794 560pM | C9 | kondenzátor keramický |

| polovodičové prvky | |||

| integrované obvody | |||

| 1 | MH 3205 | D6A | dekodér 1 z 8 |

| 2 | MH 3216 | D4A,D5A | budič/přijímač |

| 1 | UCY 7406 | D1A | 6 x invertor |

| 1 | MH 7474 | D3D | 2 x klopný obvod D |

| 1 | UCY 7485 | D7A | 4 bitový komparátor |

| 4 | UCY 74 132N | D2A,D1B,D4C,D5C | 4 x dvouvst. NAND |

| 1 | 74 180 PC | D4D | paritní generátor 8 bit |

| 4 | 75 450 PC | D1C,D2C,D1D,D2D | 2 x mezi obvodový budič |

| 1 | MHB 8255A | D3C | progr. paralelní I/O |

| 2 | KR 580 VI 53 | D2B,D3B | progr. časovaci obvod |

| 1 | K 555 LI 1 | D3A | 4 x AND |

| 1 | MHB 4049 | D4B | 6 x invertující budič |

| 1 | MAA 723CN | D5B | stabilizátor napětí |

| 1 | MA 1458 | D6B | 2 x operační zesilovač |

Schéma UDR-1 a černobílá verze ZDE.

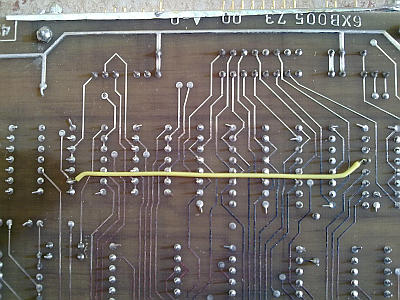

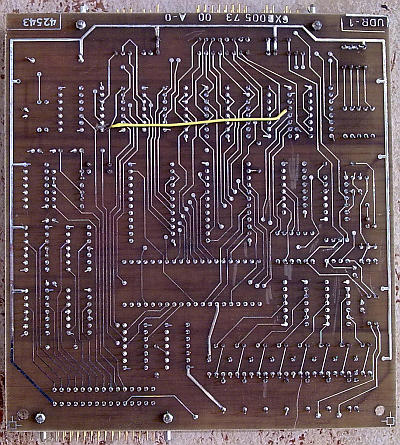

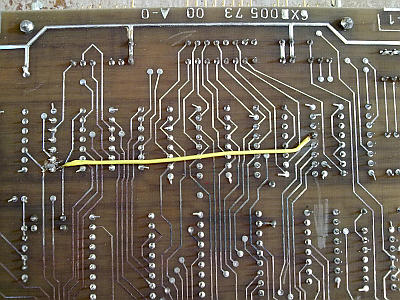

Závada na nepoužité desce

Při kontrole originál schématu vůči mnou zpětným inženýrstvím získanému schématu jsem objevil na ještě nepoužité desce zásadní závadu. Závada spočívá v tom že deska nejde adresovat. Na desce je drátový spoj odpovídací schématu, na překreslené desce je spoj již integrován do DPS. Drátový spoj se dodělával pravděpodobně až na hotové desce, kdy někdo odflákl svou práci a propojil výstup dekodéru 3205 D6A/12 (Y3) s jeho vstupem 6 (G1) a to na hradle 74132 D2A/1,2. Náprava spočívá v tom ze drátová propojka zakončená na hradle 74132 D2A se přepojí z vývodu 2 na vývod 1 pokut tam již není umístěna a spoj mezi vývody 1 a 2 ze strany pájení proškrábnout čímž se docílí stav odpovídající schématu a dokumentaci. U desek co jsem měl možnost zkontrolovat byla závada zjištěna u výrobních čísel 0402 a 0345, u výrobních čísel 0043, 0057, 0053 a 0176 je úprava provedena správně.

Technické porno

Stav před opravou

|

|

Stav po opravě

|

|

Obsah:

- Úvod

- Technické parametry

- Popis funkce

- Programováni

- Instalace

- Testováni

- Údržba a servis

- Všeobecné údaje