OCR návodu DPP-1

SAPI-1

DESKA PARALELNÍCH PORTŮ

DPP-1

6XV 122 11

6XK 199 19

TESLA ELSTROJ TESLA LIBEREC TESLA ELTOS-DIZ

Obsah:

- Úvod

- Technické parametry

- Popis funkce

- Programování

- Instalace

- Testováni

- Údržba a servis

- Všeobecné údaje

Přílohy:

- Tabulka konektoru X1

- Tabulka konektoru X2

- Tabulka konektoru X3

- Rozpiska součástí

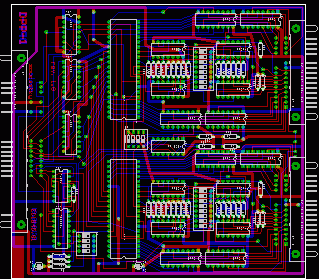

- Výkres osazeni

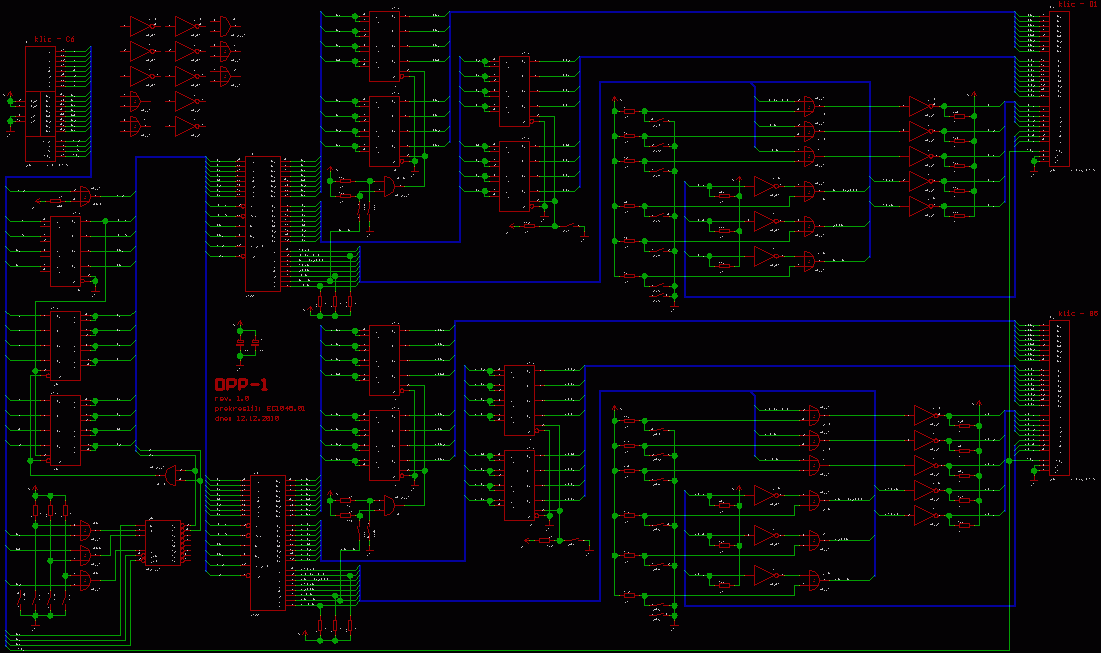

- Elektrické schéma

ÚVOD

TECHNICKÉ PARAMETRY

POPIS FUNKCE

- Adresace desky DPP-1

- Programováni desky DPP-1

- Popis módů /pracovních režimů/

- Mód 0 - základní vstup/výstupní operace

- Mód 1 - strobovaný vstup/výstup

- Mód 2 - strobovaná obousměrná sběrnice

- Stavové slovo

PROGRAMOVÁNÍ

INSTALACE

Desku paralelních portů DPP-1 vyjmeme z obalu a zkontrolujeme, zda nedošlo k poškozeni desky PS nebo kontaktů FRB konektorů. Obal uložíme pro případ zasláni desky do opravy.

Zkontrolujeme, zda připojením desky DPP-1 k souboru SAPI-1 nedojde k překročení povoleného odběru proudu ze zdroje + 5 V.

Připojeni periférií k desce DPP-1.

Pomocí přepínače S1 nastavíme adresový prostor desky DPP-1 /viz tab.2/.

Pomocí přepínačů S2, S3 a S4 nastavíme porty PA a PB do módů 0, 1 a 2 /viz tab. 7, 8 a 9/.

Pomocí přepínačů S3 a S4 nastavíme polaritu řídicích signálů portů PC /viz tab. 6/.

TESTOVÁNÍ

ŮDRŽBA A SERVIS

- Údržba

- Servis

VŠEOBECNÉ ŮDAJE

Pracovní podmínky

Kryti dle ČSN 33 0330 je IP 00

Deska paralelních portů DPP-1 je napájena ze zdroje, který odpovídá ČSN 36 9060 - Počítače a systémy zpracování dat - požadavky na el. a mech. bezpečnost a metody zkoušek.

- Kvalifikace obsluhy a údržby:

- Skladováni

- Záruka

Deska paralelních portů DPP-1 umožňuje připojeni zařízení s paralelním přenosem dat k systému SAPI-1. Rozšiřuje možnosti připojení o dalších šest jednoduchých vstupních/výstupních portů nebo čtyři strobované vstupní/výstupní porty nebo dvě obousměrné sběrnice, případně kombinace výše uvedených možností.

Předpokládaná aplikace je např. připojení terminálu s paralelním přenosem, snímače a děrovače děrné pásky, sériové tiskárny nebo číslicově řízených strojů. Univerzální použití desky paralelních portů je umožněno programovou volitelností funkce obvodů MHB 8255A, které tvoři jádro zapojeni s možnosti volby polarity řídicích signálů pro přenos dat.

Deska DPP-1 má standardní rozměr 140 x 150 mm a je opatřena třemi FRB konektory. Konektor X1 slouží pro připojení desky na sběrnici ARB-1, konektory X2 a X3 jsou určeny pro připojeni přídavných zařízení.

| Napájení desky | + 5 V ± 0,25 V |

| Odběr proudu | 1,2 A |

| Rozměry desky | 140 x 150 mm |

| Hmotnost | 180 g |

| Zátěže signálů sběrnice ARB-1 /-I1L/ | |

| A0, A1, IOR, IOW | 0,25 mA |

| A3, A4, A5 | 1,6 mA |

| A2, A6, A7 | 0,25 mA |

| D0 až D7 | 0,25 mA |

| Maximální zátěže výstupů portů /I0L/ | |

| 1PA, 1PB, 2PA, 2PB | 50 mA |

| 1PC, 2PC | 16 mA |

| Maximální zátěže vstupů portů /-I1L/ | |

| 1PA, 1PB, 2PA, 2PB | 0,25 mA |

| 1PC, 2PC | 1,6 mA |

Deska paralelních portů DPP-1 je tvořena dvěma téměř shodnými kanály, které jsou od sběrnice ARB-1 odděleny obvody 3216. Dekodér adresy je tvořen obvodem 3205 /D5A/ a obvodem 7486 /D4A/, který spolu s přepínači 1S1, 2S1, 3S1 umožňují volit adresu desky DPP-1, Výstup 0 dekodéru 3205 je přiveden na vstup CS 8255 /D1B/ a výstup 1 na vstup CS 8255 /D2B/ kanálu 2.

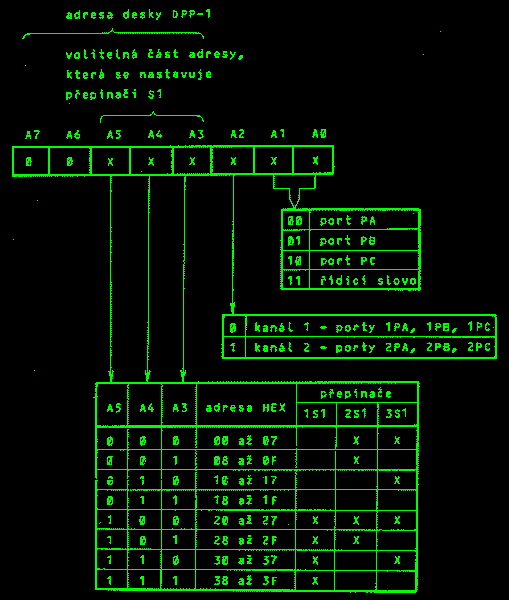

Deska DPP-1 je adresována jako vstup/výstupní zařízení. Dekódovány jsou adresy A0 až A7. Dva nejnižší bity adresové sběrnice /A0, A1/ jsou přivedeny přes obvod 3216 na adresové vstupy A0, A1 obou obvodů 8255. Zbývající bity /A2 až A7/ jsou dekódovány dekodérem 3205.

Základem obou kanálů je programovatelný obvod pro připojení periférií MHB 8255A, který obsahuje 3 osmibitové porty PA, PB, PC. Na vstupy RD a WR obou obvodů 8255 jsou přes obvod 3216 přivedeny signály IOR a IOW. Signál RESET ze sběrnice ARB-1 je invertován a je přiveden na resetovací vstupy obou obvodů 8255. Při stavu RESET = 1 se vnitřní řídící obvody 8255 nastavují do módu /pracovního režimu/ 0 pro vstup dat ve všech třech portech, přičemž všechny vnitřní registry dat se nulují. Signál CS uvádí při stavu CS = 0 obvod do funkce. Při stavu CS = 1 přechází datová sběrnice D0 až D7 do stavu vysoké impedance. Funkce signálu čtení RD, signálu zápisu WR a dvou adresových signálů A0, A1 vysvětluje následující tabulka.

| CS | A1 | A0 | RD | WR | funkce |

| 1 | X | X | X | X | stav vysoké impedance |

| 0 | 0 | 0 | 1 | 0 | zápis do portu PA |

| 0 | 0 | 1 | 1 | 0 | zápis do portu PB |

| 0 | 1 | 0 | 1 | 0 | zápis do portu PC |

| 0 | 1 | 1 | 1 | 0 | zápis řídicího slova |

| 0 | 0 | 0 | 0 | 1 | čtení portu PA |

| 0 | 0 | 1 | 0 | 1 | čtení portu PB |

| 0 | 1 | 0 | 0 | 1 | čtení portu PC |

| 0 | 1 | 1 | 0 | 1 | nepřípustná podmínka |

Tab.1: Funkce signálů RD, WR, A0, A1

Porty PA a PB jsou od konektorů X2, X3 odděleny obvody 3216. Směr toku dat přes tyto obvody je určen nastavením přepínačů - lze tedy volit směr toku dat porty PA a PB. Port PC má některé bity pevně zapojené jako vstupní, jiné jako výstupní. Výstupní bity /PCO, PC1, PC3, PCS a PC7/ jsou ošetřeny invertory s otevřeným kolektorovým výstupem 7405. U bitů PC1, PC5 a PC7 lze pomocí přepínačů způsobit inverzi signálů. Vstupní bity portu PC /PC2, PC4, PC6/ jsou ošetřeny invertory 7404.

Přerušeni INT 0 ze sběrnice ARB-1 je vyvedeno na vývody, 18 konektorů X2, X3.

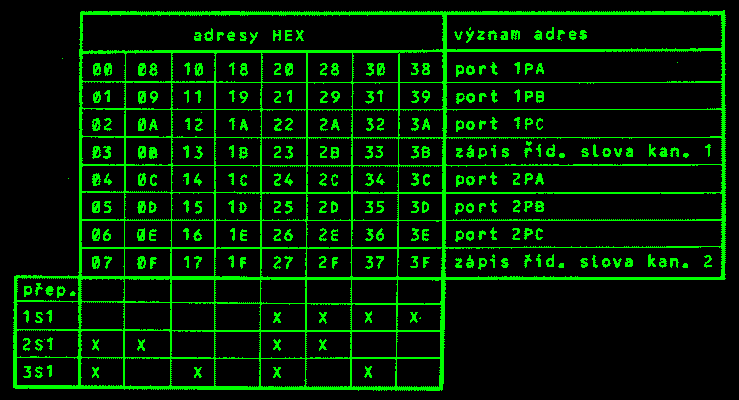

Deska DPP-1 se adresuje jako V/V zařízeni. Adresy jsou rozděleny do 8 adresových prostorů, které jsou vymezeny sloupci v tab. 2. Volba těchto prostorů se provádí nastavením přepínačů S1 podle spodní části tabulky. Řádky v tabulce popisují významy jednotlivých adres.

Tab. 2: Adresace desky DPP-1 /hexadecimálně/

Tabulka 3 popisuje adresaci desky DPP-1 binárně. Obsahově je shodná s tabulkou 2.

Tab. 3: Adresace desky DPP-1 /binárně/

Funkční vlastnosti obou kanálů jsou z velké části určeny vlastnostmi obvodu 8255. Proto bude další popis funkce desky DPP-1 zaměřen na popis obvodu 8255 s přihlédnutím ke konkrétnímu zapojeni na desce DPP-1.

Obvod MHB 8255A je programovatelný víceúčelový obvod pro připojeni vstupů/výstupů k mikroprocesoru 8080. Může pracovat ve třech pracovních režimech /módech/. Obsahuje 24 vstupů/výstupů, která jsou programovány odděleně ve dvou skupinách /A, B/ po 12, přičemž jsou rozděleny do tří osmibitových portů PA, PB, PC /port PC lze rozdělit na dva čtyřbitová porty s rozdílným směrem přenosu/.

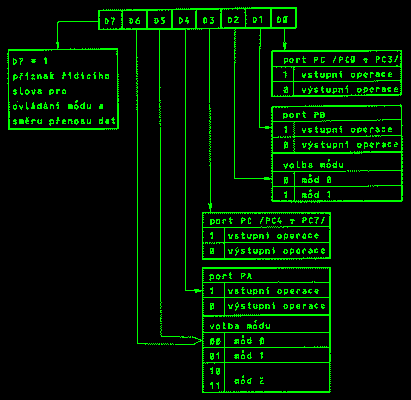

Funkce každého jednotlivého portu se naprogramuje vysláním řídicího slova pro ovládáni módu a směru přenosu dat. Význam jednotlivých bitů tohoto řídicího slova je popsán v tab. 4.

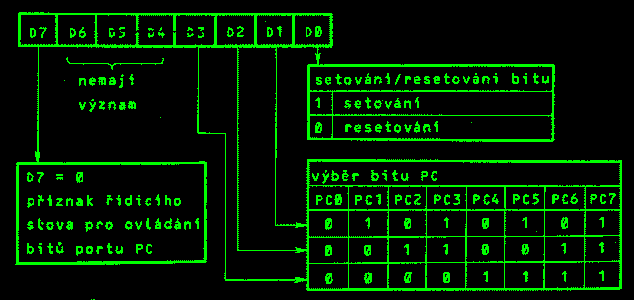

Do jednotlivých bitů portů PC lze zadávat požadované logické stavy /setováním, resetovánim/ individuálně a to pomoci řídicího slova pro ovládáni bitů portu PC. Význam jednotlivých bitů tohoto řídicího slova je popsán v tab. 5.

Oba druhy řídicích slov /pro ovládáni módu i pro ovládání bitů portu PC/ se zapisují na adresy, popsané v tab.2.

Upozorněni: Popis logických stavů bitů portů PC /např. v tab. 5/ je definován vzhledem k výstupu 8255. Je proto nutné vzít v úvahu konkrétní zapojeni portů PC - popsáno v tab.6.

Tab. 4: Řídicí slovo pro ovládání módu a směru přenosu dat

Tab. 5: Řídicí slovo pro ovládání portu PC

| bit | operace | ovlivnění inverze přepínačem | vývod konektoru |

| 1PC0 | výstupní | trvale inverzní | X2/11 |

| 1PC1 | výstupní | 4S3 | X2/12 |

| 1PC2 | vstupní | 3S3 | X2/16 |

| 1PC3 | výstupní | trvale inverzní | X2/13 |

| 1PC4 | vstupní | 2S3 | X2/15 |

| 1PC5 | výstupní | 5S3 | X2/10 |

| 1PC6 | vstupní | 6S3 | X2/14 |

| 1PC7 | výstupní | 7S3 | X2/9 |

| 2PC0 | výstupní | trvale inverzní | X3/11 |

| 2PC1 | výstupní | 4S4 | X3/12 |

| 2PC2 | vstupní | 3S4 | X3/16 |

| 2PC3 | výstupní | trvale inverzní | X3/13 |

| 2PC4 | vstupní | 2S4 | X3/15 |

| 2PC5 | výstupní | 5S4 | X3/10 |

| 2PC6 | vstupní | 6S4 | X3/14 |

| 2PC7 | výstupní | 7S4 | X3/9 |

Ve sloupci ovlivnění inverze přepínačem je uveden přepínač, při jehož sepnutí je signál na příslušném vývodu vstup/výstupních konektorů /X2, X3/ vzhledem k výstupu 8255 inverzní. Při rozepnutém přepínači není inverzní.

Tab. 6: Zapojeni portů PC.

Vlastnosti obvodu 8255 jej dovolují programovat ve dvou samostatných skupinách A, B /viz tab.4/ do nezávislých funkčních režimů - módů.

Skupina A obsahuje osmibitový port PA a vyšší čtyři bity portu PC /PC4 až PC7/ a může být programována do módů 0, 1, 2. Skupina B obsahuje osmibitový port PB a nižší čtyři bity portu PC /PC0 až PC3/ a může být programována do módů 0 a 1. Programování obou skupin je nezávislé.

Všech 24 vstupů/výstupů je uspořádáno do tři osmibitových portů PA, PB, PC /port PC v módu 0 lze využít jako dva čtyřbitové porty/. Všechny vodiče portů u obvodu 8255 mohou být využity pro přenos dat, žádný negeneruje ani nepřijímá korespondenční signály přenosu, takže jde o přenos bez potvrzení.

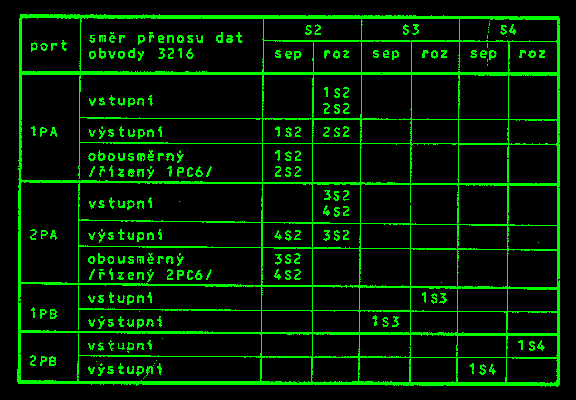

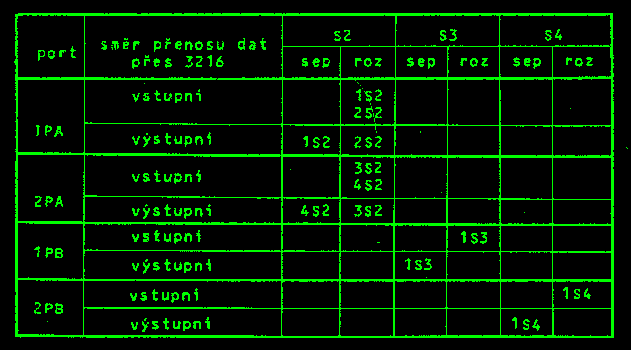

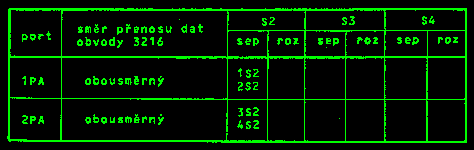

Aby byla zaručena správná funkce desky DPP-1, musí být směr přenosu dat porty PA a PB obvodu 8255 /nastavený řídícím slovem pro ovládáni módu a směru přenosu dat/ v souladu s nastavením směru přenosu dat obvody 3216. Nastaveni směru přenosu dat obvody 3216 pomocí přepínačů je popsáno v tab. 7.

Tab. 7: Nastavení směru přenosu dat obvody 3216 - mód 0

Při obousměrném přenosu dat obvody 3216 se směr přenosu dat řídí bitem 1PC6 přivedeným na X2/14 pro 1PA a bitem 2PC6 přivedeným na X3/14 pro 2PA. Je třeba zajistit, aby nedocházelo ke konfliktům logických úrovni mezi jednotlivými bity portů PC a ošetřujícími obvody /viz el. schéma desky DPP-1 a tab. 6/.

Konkrétní zapojeni jednotlivých bitů portu PC /PC2, PC4, PC6 trvale vstupní, ostatní trvale výstupní/ omezuje využitelnost portů PC v módu 0. Pokud přesto budou využívány v módu 0, je opět nutné zajistit, aby nedocházelo ke konfliktům logických úrovní.

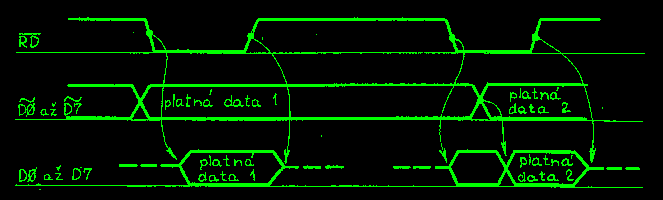

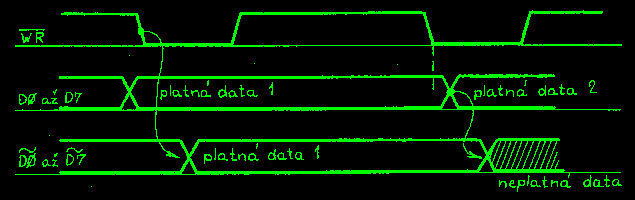

Časové závislosti v módu 0

Obr. 1: Časový diagram činnosti v módu 0 vstupní operace

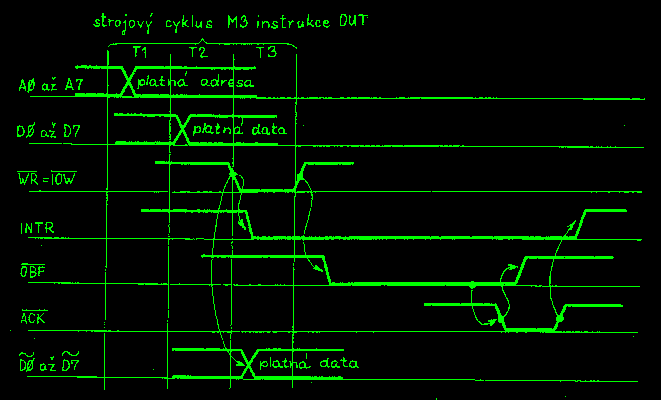

Obr. 2: časový diagram činností v módu 0 výstupní operace

Vstupní operace /viz obr. 1/

Při vstupní operaci jsou data ze sběrnice periférie /D0~ až D7~/ připojována na datovou sběrnici mikroprocesoru /ARB-1/ signálem RD, přičemž není ve funkci vyrovnávací registr obvodu. Proto je možné dodat platná data na sběrnici periférie až po dodrženi požadavků procesoru na přítomnost vstupních dat na sběrnici. Tento stav je naznačen ve druhé části časového diagramu. Mimo platnost vztahu RD = O je datová sběrnice /D0 až D7/ ve stavu vysoké impedance, aby neovlivnila probíhající provoz mikroprocesoru s dalšími elementy mikropočítače.

Výstupní operace /viz obr. 2/

Při výstupní operaci jsou data z datové sběrnice /D0 až D7/ přepisována úrovní WR = 0 do výstupního vyrovnávacího registru V/V kanálu, jehož výstupy tvoři datovou sběrnici periférie /D0~ až D7~/. Nedodržení potřebného předstihu a přesahu výstupních dat vzhledem k časování signálu WR může vést k hazardním stavům na výstupu V/V kanálu.

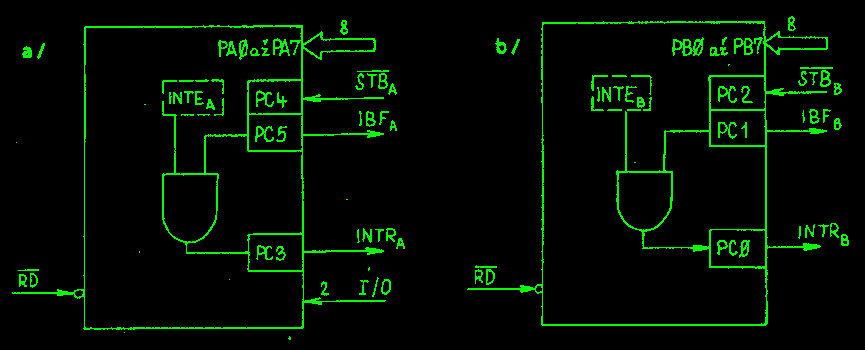

Mód 1 slouží k výměně dat mezi vstupy/výstupy do nebo ze zvoleného portu ve spojení se strobovacími impulsy nebo signály pro potvrzení.

Porty PA, PB v módu 1 mohou být programovány jako vstupní nebo výstupní. Aby byla zaručena správná funkce desky DPP-1, musí být smě přenosu dat porty PA, PB obvodu 8255 /nastavený řídícím slovem pro ovládání módu a směru přenosu dat/ v souladu s nastavením směru přenosu dat obvody 3216. Nastavení směru přenosu dat obvody 3216 pomoci přepínačů je popsáno v tab. 8.v módu 1 není možné použít bit lPC6 ani 2PC6 k řízení směru přenosu dat obvody 3216, protože dochází ke konfliktům logických úrovní mezi 8255 a obvody 3216.

Tab. 8: Nastavení směru přenosu dat přes obvody 3216 - mód 1

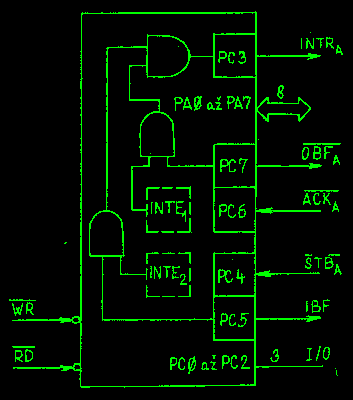

Rozdělení portů PC na vyšší polovinu /bity PC4 až PC7/ a nižší polovinu /bity PC0 až PC3/ je porušeno. Vždy tři bity z každé poloviny se používají pro výměnu potvrzení přenosu dat a generování požadavku přerušení do mikropočítače. Zbývající dva bity portu PC patří vždy do vyšší poloviny a jsou programovatelné /směr přenosu/ v módu 0 ve skupině A /viz obr. 3 a 4/. V módu 1 se činnost korespondenčních vodičů vzniklých z bitů portu PC nemusí zvlášť programovat, neboť jde o funkce dané vnitřním zapojením obvodu.

Definice řídicích signálů:

a/ vstupní operace

| STB /STROBE/ | - strobovací vstup |

| - při stavu STB = 0 se data z periférie zapisují do vstupního registru obvodu 8255 | |

| IBF /INPUT BUFFER FULL/ | - indikace naplněni vstupního registru |

| - úroveň signálu IBF = 1 na tomto výstupu signalizuje, že data byla uložena do vstupního registru, odpovídá potvrzeni. | |

| - IBF je setován /IBF = 1/ sestupnou hranou signálu STB a je resetován /IBF = 0/ náběžnou hranou čtecího signálu z procesoru RD. | |

| INTR /INTERRUPT/ | - požadavek přerušeni pro procesor |

| - je setován /INTR = 1/ při náběžné hraně signálu STB a resetován /INTR = 0/ při sestupné hraně signálu RD. | |

| - signál INTR je funkční pouze při IBF = 1 a při nastavené masce přerušeni INTE. Ta se nastavuje programováním stavu bitu PC4 /pro port PA/ a bitu PC2 /pro port PB/. | |

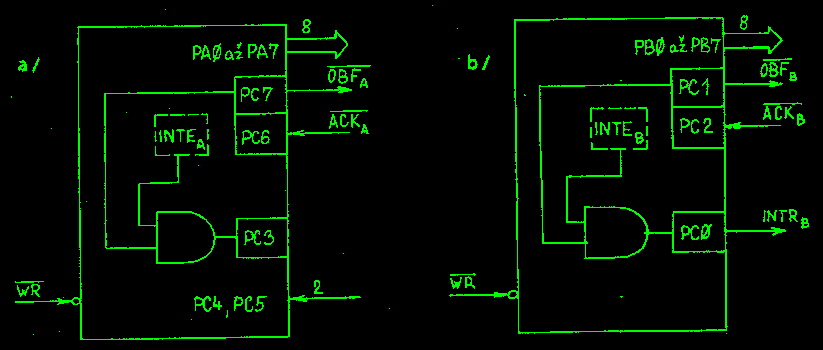

b/ výstupní operace

| OBF /OUTPUT BUFFER FULL/ | - indikace naplněni výstupního registru |

| - signál OBF je resetován /OBF = 0/ při zápisu dat z procesoru do výstupního registru /= sestupná hrana signálu WR/ a setován / OBF = 1/ při náběžné hraně potvrzovacího signálu ACK od periférie | |

| ACK /ACKNOWLEDGE/ | - potvrzeni výstupu od periférie |

| - výstupní zařízení potvrdí převzetí dat signálem ACK = 0. Převzetí dat uvolní výstupní registr /OBF _ > 1/ a vyvolá nový požadavek přerušeni /INTR _> 1/ | |

| INTR /INTERRUPT/ | - požadavek přerušení pro procesor |

| - signál INTR je setován /INTR = 1/ při náběžné hraně signálu ACK a resetován při sestupné hraně signálu WR | |

| - signál INTR je funkční pouze při OBF = 1 a při nastavené masce přerušení INTE. Ta se nastavuje programováním stavu bitu PC6 /pro port PA/ a bitu PC2 /pro port PB/ | |

V módu 1 s výhodou využijeme zapojeni jednotlivých bitů portů PC. Toto zapojení umožňuje invertovat signály jednotlivých bitů pomoci přepínačů. V textu popisu módu 1 byly tyto signály popsány vzhledem k výstupu 8255. V konkrétních případech je třeba brát v úvahu vliv zapojení portů PC /tab. 6/.

Varianty činnosti v módu 1:

Porty PA a PB mohou být v módu 1 definovány nezávisle na sobě jako vstupy nebo jako výstupy, tím je dána možnost strobovaných vstupů a výstupů.

| Obr. 3: | Mód 1 - vstupní operace |

| a/ port PA | |

| b/ port PB | |

| pozn.: INTE = vnitřní klopný obvod pro nastavení masky přerušení |

| Obr. 4: | Mód 1 - výstupní operace |

| a/ port PA | |

| b/ port PB | |

| pozn.: INTE = vnitřní klopný obvod pro nastavení masky přerušení |

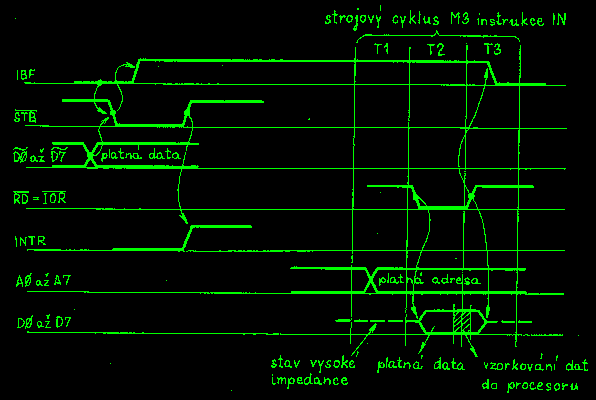

Časové závislosti v módu 1

a/ vstupní operace

Obr. 5: Časový diagram činnosti v módu 1 - vstupní operace

V první části časového diagramu je naznačena aktivita vstupní periférie. Výsledkem této aktivity je naplnění vstupního vyrovnávacího registru portů platnými daty a generováni požadavku přerušení. Ve druhé části diagramu je naznačena reakce procesoru na požadavek přerušení. Výsledkem činnosti procesoru je přenos platných dat do vnitřního registru portů a zrušení požadavku přerušení.

Signál IBF hlásí vstupní periférii, že může zahájit přenos dalšího slova dat. Nedodržení pokynu signálem IBF /vyslání signálu STB = 0 při IBF = 1/ může vést ke ztrátě platnosti dat ve vstupním vyrovnávacím registru portů. Ve druhé části časového diagramu je patrné ovládání datové sběrnice D0 až D7 signálem RD. Tento signál vyvádí sběrnici ze stavu vysoké impedance pouze na dobu nezbytně nutnou k převzetí dat do procesoru.

b/ výstupní operace

Obr. 6: Časový diagram činností v módu 1 - výstupní operace

Při výstupní operaci je v první části časového diagramu naznačena činnost procesoru, spočívající v přenosu slova dat do výstupního vyrovnávacího registru portů a ve zrušení požadavku přerušení od výstupní periférie. Ve druhé části je naznačena reakce výstupní periférie na úroveň OBF - 0. Po převzetí slova dat výstupní periférie obnovuje požadavek přerušení.

Vznik požadavku přerušeni a jeho zpracováni je opět volně svázáno přes programové ošetření. Jestliže procesor zapisuje nové slovo dat do vyrovnávacího registru portů během trváni signálu OBF - 0, dochází ke ztrátě platnosti výstupních dat. Výstupní sběrnice periférie nepřechází do stavu vysoké impedance, pouze se na ní objevuji nově zapisovaná platná data k procesoru.

Slouží k výměně dat s periferním zařízením na osmibitové obousměrné sběrnici, přes kterou jsou data přijímána a vysílána. V módu 2 lze využit pouze porty PA a PC, přičemž PA slouží k přenosu dat a pět bitů portu PC nabývá funkci korespondenčních signálů pro organizaci přenosu /viz obr. 7/.

Význam řídicích signálů je stejný jako u módu 1 a jejich soubor je sjednocením souboru vstupních a výstupních řídicích signálů módu 1.

Obr. 7. Mód 2 - obousměrná sběrnice

Tab. 9: nastaveni směru přenosu dat obvody 3216 - mód 2

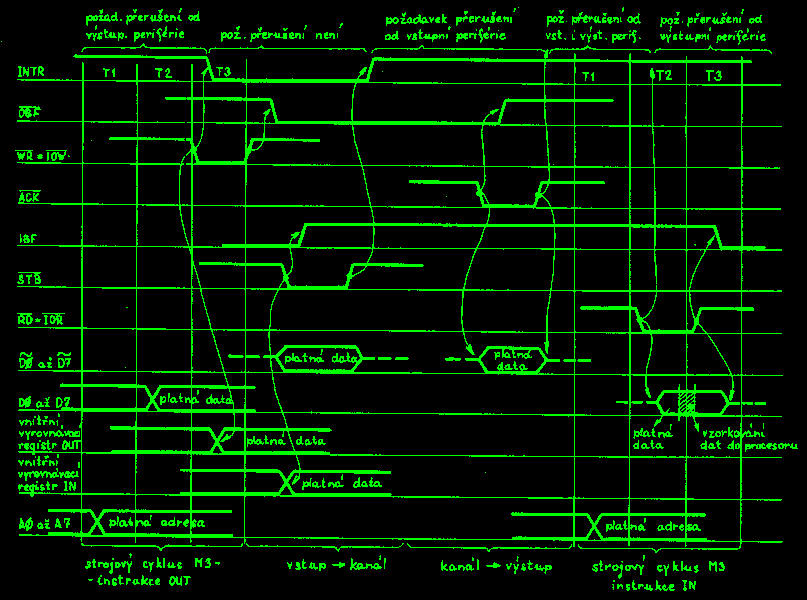

Časové závislosti v módu 2 /viz obr. 8/

Časový diagram má čtyři části volně na sebe navazující přes programové vybaveni procesoru a fyzikální vlastnosti V/V zařízení. V první části zapisuje procesor data do vstupního vyrovnávacího registru a ruší požadavek přerušeni. Ve druhé části zapisuje vstupní periférie data do vstupního vyrovnávacího registru a generuje požadavek přerušeni do procesoru.Ve třetí části přebírá výstupní periférie data z V/V kanálu a generuje požadavek přerušení do procesoru. Čtvrtá část časového diagramu zobrazuje převzetí slova dat do procesoru. přitom však zůstává aktivován požadavek přerušení. Je tomu tak proto, že signál INTR je logickým součtem požadavků přerušení od vstupního a výstupního zařízení. Po ukončení přenosu dat do procesoru ve čtvrté části časového diagramu zůstává nastaven požadavek přerušení od výstupní periférie. V časovém úseku mezi druhou a třetí části diagramu jsou obě přerušená slova uchovávána ve vyrovnávacích registrech, Platná data jsou vymezena podmínkou ACK = 0. U časového průběhu požadavku přerušeni INTR jsou uvedeny zdroje tohoto požadavku.

V módu 2 s výhodou využijeme zapojení jednotlivých bitů portů PC na desce DPP -·1. Toto zapojení umožňuje invertovat signály jednotlivých bitů pomoci přepínačů. V textu popisu módu 2 byly popsány tyto signály vzhledem k výstupu 8255. V konkrétních případech je třeba brát v úvahu vliv zapojení jednotlivých bitů portů PC /tab. 6/.

Obr. 8: Časový diagram činností v módu 2

V těch funkčních režimech, kdy se vodiče portu PC podílejí na organizaci přenosu dat a nemají význam dat, je operace čteni portu PC využita pro přenos stavového slova obvodu. Při kombinovaných módech nebo při programování portu PA v módu 1 - vstupní operace obsahuje slovo přečtené z portu PC kromě stavových bitů také bity dat. Stavové bity soustředěné ve stavových slovech charakterizují svými hodnotami okamžitý stav výměny dat mezi obvodem 8255 a připojenými V/V zařízeními. Vyhodnocení stavových slov programem může proto poskytovat informace využitelné pro větveni programu apod.

| mód 1 | ||||||||

| port PA | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| vst. operace | V/V | V/V | IBFA | INTEA | INTRA | |||

| mód 1 | ||||||||

| port PA | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| výst. operace | OBFA | INTEA | V/V | V/V | INTRA | |||

| mód 1 | ||||||||

| port PB | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| vst. operace | INTEB | IBFB | INTRB | |||||

| mód 1 | ||||||||

| port PB | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| výst. operace | INTEB | OBFB | INTRB | |||||

| mód 2 | ||||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| OBFA | INTE1 | IBFA | INTE2 | INTRA | ||||

| OUT | IN |

Obr. 9: Části stavového slova

Pozn. - celkové stavové slovo je pak kombinací některých uvedených části nebo některé uvedené části s danou části čtenou z portu PC pracujícího v módu 0 - vstupní operace.

Programování desky DPP-1 je zřejmé z funkčního popisu. Pro názornost uvádíme příklad:

Nechť je adresový prostor do něhož je deska adresována 10H až 17H.

Port 1PA bude pracovat v módu 2, port 1PB v módu 0 - vstupní operace a bit 1PC2 v módu 0 - vstupní operace. Přerušení při vstupu i výstupu dat portu 1PA bude povoleno.

Port 2PA bude pracovat v módu 1 - výstupní operace, port 2PB v módu 1 - vstupní operace a bit 2PC4 v módu 0 - vstupní operace. Přerušeni kanálu 2 /portů 2PA a 2PB/ nebudou využity.

stroj.

adr. kód symbolická

/hex/ /hex/ instrukce význam

;Kanál 1 /porty 1PA, 1PB, 1PC/

0000 3E EB MVI A EBH ;říd. slovo pro nastaveni módu a směru přenosu dat -> akumulátor

0002 D3 13 OUT 13H ;nastavení říd. slova pro nastaveni módu a směru přenosu dat

0004 3E 09 MVI A,09 ;říd. slovo pro ovládání bitů portu PC -> akumulátor

0006 D3 13 OUT 13H ;nastavení INTE2 - povoleni přerušení při vstupu 1PA

0008 3E 8D MVI A,0DH ;říd. slovo pro ovládání bitů portu PC -> akumulátor

000A D3 13 0UT 13H ;nastavení INTE1 - povoleni přerušeni při výstupu 1PA

;Kanál 2 /porty 2PA, 2PB, 2PC/

000C 3E 8F MVI A,BFH ;říd. slovo pro nastavení módu a směru přenosu dat--> akumulátor

000E D3 17 0UT 17H ;nastavení řídicího slova pro nastaveni módu a směru přenosu dat

......

Při čtení a zápisu dat v módech 1 a 2 lze použit dvojí způsob programovacích technik:

V prvém čteme port PC a testujeme stav bitů odpovídajících , signálům IBF a OBF /nelze ACK a STB/ a podle jejich stavu provádíme čteni nebo další zápis dat.

V druhém případě signál INTR - vstupní žádá o čteni dat a signál INTR - výstupní ve stavu 0 /na výstupu desky/ povoluje další zápis dat.

Zkontrolujeme, zda odběry periferních zařízení, které chceme připojit k desce DPP-1 nepřekračuji povolené zátěže desky.

Zkontrolujeme, zda signály přivedené na vstupy desky DPP-1 jsou v úrovních TTL.

Zkontrolujeme, zda připojená zařízení odpovídají ČSN 36 9060 - Počítače a systémy pro zpracování dat - požadavky na elektrickou a mechanickou bezpečnost a metody zkoušek.

Funkce desky paralelních portů DPP-1 je ve výrobním podniku kontrolována pomoci testu TSX 05 v konfiguraci SAPI-1.

Údržba desky paralelních portů DPP-1 spočívá v udržováni kontaktů FRB konektorů. Aby byla zajištěna spolehlivá činnost systému, je nutné chránit kontakty FRB konektorů před znečištěním a mechanickým poškozením. Před každým zasunutím desky do sběrnice systému SAPI-1 je nutné zkontrolovat, zda nejsou vývody konektorů FRB ohnuty, aby nedošlo k jejich ulomeni.

servis desky paralelních portů zajišťuje dodavatel Tesla DIZ prostřednictvím servisních středisek. Při odesílání desky do opravy je nutné ji zabalit do původního přepravního obalu.

| Teplota okolí | + 5°C až + 40°C |

| Relativní vlhkost | 40% až 80% při 30°C |

| Prostředí | neklimatizované, bez agresivních plynů a par |

| Atmosférický tlak | 84 až 107 kPa |

| Prašnost prostředí | max. 1 mg/m3, velikost částic max. 10 µm |

| Odolnost proti vibracím | 0,1 mm při 25 Hz |

pracovník poučený dle § 4 vyhlášky 50/78 Sb.

Skladovací prostor musí být suchý, dobře větraný,bez mechanických otřesů a chemických vlivů. Skladovací teplota musí být v rozmezí - 5°C až + 35°C a relativní vlhkost nesmí překročit 75%. Deska musí být skladována v neporušeném obalu. Při vybalováni desky /zvláště v zimním období/ je nutné ji ponechat v přepravním obalu 4 až 5 hodin v pracovních podmínkách, aby se vyrovnaly teploty uvnitř a vně obalů a tím se zabránilo orosení desky.

Výrobce ručí za jakost výrobku po dobu 6 měsíců ode dne uvedeni do provozu za předpokladu, že deska nebyla poškozena hrubým nebo neodborným zásahem.

Příloha : Tabulka konektoru X1

Příloha : Tabulka konektoru X2

Příloha : Tabulka konektoru X3

Příloha : Rozpiska součásti

Příloha: Rozmístění součástek

Příloha: Schéma zapojení

Deska: DPP-1 Konektor: X1 Klíč: C6 Typ: TY 517 6211

Protikus: Sběrnice ARB-1 Konektor X2 až X8

| č. | signál | význam | typ | č. | signál | význam | typ | |

| 1 | 2 | |||||||

| 3 | 4 | |||||||

| 5 | 6 | |||||||

| 7 | 8 | RES | nulování | INP | ||||

| 9 | 10 | IOR | čteni z portu | INP | ||||

| 11 | 12 | IOW | zápis do portu | INP | ||||

| 13 | 14 | |||||||

| 15 | +5V | napájení | NAP | 16 | +5V | napájeni | NAP | |

| 17 | 18 | |||||||

| 19 | 0V | zem | NAP | 20 | 0V | zem | NAP | |

| 21 | 22 | |||||||

| 23 | 24 | |||||||

| 25 | 26 | |||||||

| 27 | 28 | |||||||

| 29 | 30 | |||||||

| 31 | D4 | data | I/O | 32 | D3 | data | I/O | |

| 33 | D6 | data | I/O | 34 | D5 | data | I/O | |

| 35 | D2 | data | I/O | 36 | D7 | data | I/O | |

| 37 | D0 | data | I/O | 38 | D1 | data | I/O | |

| 39 | A1 | adresa | INP | 40 | A0 | adresa | INP | |

| 41 | A3 | adresa | INP | 42 | A2 | adresa | INP | |

| 43 | A5 | adresa | INP | 44 | A4 | adresa | INP | |

| 45 | A7 | adresa | INP | 46 | A6 | adresa | INP | |

| 47 | 48 | |||||||

| 49 | 50 | |||||||

| 51 | 52 | |||||||

| 53 | 54 | |||||||

| 55 | 56 | |||||||

| 57 | 58 | |||||||

| 59 | 60 | |||||||

| 61 | 62 | INT0 | žádost o přeruš. | INP | ||||

| Typ signálu: | INP | vstupní |

| OUT | výstupní | |

| I/O | obousměrný | |

| NAP | napájeni | |

Deska: DPP-1 Konektor: X2 Klíč: D1 Typ: TY 513 3011

Protikus: 30-pólová zásuvka FRB / _> přídavné zařízení/

| č. | signál | význam | typ | č. | signál | význam | typ | |

| 1 | 1PA5 | port 1PA | I/O | 2 | 1PA0 | port 1PA | I/O | |

| 3 | 1PA2 | port 1PA | I/O | 4 | 1PA7 | port 1PA | I/O | |

| 5 | 1PA4 | port 1PA | I/O | 6 | 1PA6 | port 1PA | I/O | |

| 7 | 1PA3 | port 1PA | I/O | 8 | 1PA1 | port 1PA | I/O | |

| 9 | 1PC7 | OBFA | OUT | 10 | 1PC5 | IBFA | OUT | |

| 11 | 1PC0 | INTRB | OUT | 12 | 1PC1 | IBFB, OBFB | OUT | |

| 13 | 1PC3 | INTRA | OUT | 14 | 1PC6 | ACKA | INP | |

| 15 | 1PC4 | STBA | INP | 16 | 1PC2 | ACKB, STBB | INP | |

| 17 | 0V | zem | NAP | 18 | INT0 | žádost o přeruš. | INP | |

| 19 | 0V | zem | NAP | 20 | ||||

| 21 | 22 | |||||||

| 23 | 1PB2 | port 1PB | I/O | 24 | 1PB6 | port 1PB | I/O | |

| 25 | 1PB5 | port 1PB | I/O | 26 | 1PB1 | port 1PB | I/O | |

| 27 | 1PB3 | port 1PB | I/O | 28 | 1PB0 | port 1PB | I/O | |

| 29 | 1PB4 | port 1PB | I/O | 30 | 1PB7 | port 1PB | I/O | |

| Typ signálu: | INP | vstupní |

| OUT | výstupní | |

| I/O | obousměrný | |

| NAP | napájeni | |

Pozn. jednotlivé bity portu PC mohou mít kromě významu bitů dat /jako porty PA a PB/ také význam stavových bitů. Proto jsou ve sloupci "význam" uvedeny příslušné řadicí signály přenášené bity portu PC. Polarita těchto signálů je uvedena při rozepnutých přepínačích 2S3 až 7S3.

Deska: DPP-1 Konektor: X3 Klíč: B5 Typ: TY 513 3011

Protikus: 30-pólová zásuvka FRB / _> přídavné zařízení/

| č. | signál | význam | typ | č. | signál | význam | typ | |

| 1 | 2PA5 | port 2PA | I/O | 2 | 2PA0 | port 2PA | I/O | |

| 3 | 2PA2 | port 2PA | I/O | 4 | 2PA7 | port 2PA | I/O | |

| 5 | 2PA4 | port 2PA | I/O | 6 | 2PA6 | port 2PA | I/O | |

| 7 | 2PA3 | port 2PA | I/O | 8 | 2PA1 | port 2PA | I/O | |

| 9 | 2PC7 | OBFA | OUT | 10 | 2PC5 | IBFA | OUT | |

| 11 | 2PC0 | INTRB | OUT | 12 | 2PC1 | IBFB, OBFB | OUT | |

| 13 | 2PC3 | INTRA | OUT | 14 | 2PC6 | ACKA | INP | |

| 15 | 2PC4 | STBA | INP | 16 | 2PC2 | ACKB, STBB | INP | |

| 17 | 0V | zem | NAP | 18 | INT0 | žádost o přeruš. | INP | |

| 19 | 0V | zem | NAP | 20 | ||||

| 21 | 22 | |||||||

| 23 | 2PB2 | port 2PB | I/O | 24 | 2PB6 | port 2PB | I/O | |

| 25 | 2PB5 | port 2PB | I/O | 26 | 2PB1 | port 2PB | I/O | |

| 27 | 2PB3 | port 2PB | I/O | 28 | 2PB0 | port 2PB | I/O | |

| 29 | 2PB4 | port 2PB | I/O | 30 | 2PB7 | port 2PB | I/O | |

| Typ signálu: | INP | vstupní |

| OUT | výstupní | |

| I/O | obousměrný | |

| NAP | napájeni | |

Pozn. jednotlivé bity portu PC mohou mít kromě významu bitů dat /jako porty PA a PB/ také význam stavových bitů. Proto jsou ve sloupci "význam" uvedeny příslušné řadicí signály přenášené bity portu PC. Polarita těchto signálů je uvedena při rozepnutých přepínačích 2S4 až 7S4.

konstrukční materiál

| poč. | označení součásti | označení polohy | název |

| 1 | 6XB 005 24 | deska PS oboustranná | |

| 1 | TY 517 6211 | X1 | vidlice FRB 62 pin - uprav. |

| 2 | TY 513 3011 | X2, X3 | vidlice FRB 30 pin |

| 2 | TS 501 4141 | S1, S2 | čtyřnásobný přepínač DIL |

| 2 | TS 501 8181 | S3, S4 | osminásobný přepínač DIL |

pasivní prvky

| poč. | označení součásti | označení polohy | název |

| 10 | TR 191 1K0K | R22, R24, R26, R32, R34,R36,R38-R41 | odpor 0,25W, tolerance 10% |

| 34 | TR 191 10KK | R1-R21, R23, R25, R27-R31, R33, R35, R37,R42-R44 | odpor 0,25W, tolerance 10% |

| 2 | TE 131 6u8 | C1, C2 | kond.elektrolyt.,tantalový |

integrované obvody

| poč. | označení součásti | označení polohy | název |

| 2 | MH 7404 | D2D, D6D | 6 x invertor |

| 2 | MH 7405 | D5A, D3D | 6 x invertor s otevř.výst |

| 1 | UCY 7408 | D4C | 4 x AND |

| 5 | 7486 PC | D1C, D2C, D4A, D5C, D6C | 4 x EXCLUSIVE - OR |

| 2 | MHB 8255A | D1B, D2B | program. paralelní V/V |

| 1 | MH 3205 | D5A | dekodér 1 z osmi |

| 11 | MH 3216 | D1A, D2A, D3A, D3C, D7C, D1D, D4D, D5D, D8D, D1E, D2E | neinvertující budič/ přijímač sběrnice s třístav. výstupy |

Schéma DPP-1 a černobílá verze ZDE.

Obsah:

- Úvod

- Technické parametry

- Popis funkce

- Programování

- Instalace

- Testováni

- Údržba a servis

- Všeobecné údaje

Přílohy:

- Tabulka konektoru X1

- Tabulka konektoru X2

- Tabulka konektoru X3

- Rozpiska součástí

- Výkres osazeni

- Elektrické schéma